Datasheet 搜索 > 微控制器 > ST Microelectronics(意法半导体) > STM32F746VGT7 数据手册 > STM32F746VGT7 数据手册 149/227 页

器件3D模型

器件3D模型¥ 91.419

STM32F746VGT7 数据手册 - ST Microelectronics(意法半导体)

制造商:

ST Microelectronics(意法半导体)

分类:

微控制器

封装:

LQFP-100

描述:

ARM Cortex-M7 216MHz 闪存:1MB RAM:320KB

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P45P46P47P48P49P50P51P52P53P54P55P56Hot

典型应用电路图在P125P126P149

封装尺寸在P196P197P198P199P200P201P202P203P204P205P206P207

型号编码规则在P223

标记信息在P198P201P204P207P211P215P218P221

技术参数、封装参数在P96P137

电气规格在P94P95P96P97P98P99P100P101P102P103P104P105

导航目录

STM32F746VGT7数据手册

Page:

of 227 Go

若手册格式错乱,请下载阅览PDF原文件

DocID027590 Rev 4 149/227

STM32F745xx STM32F746xx Electrical characteristics

195

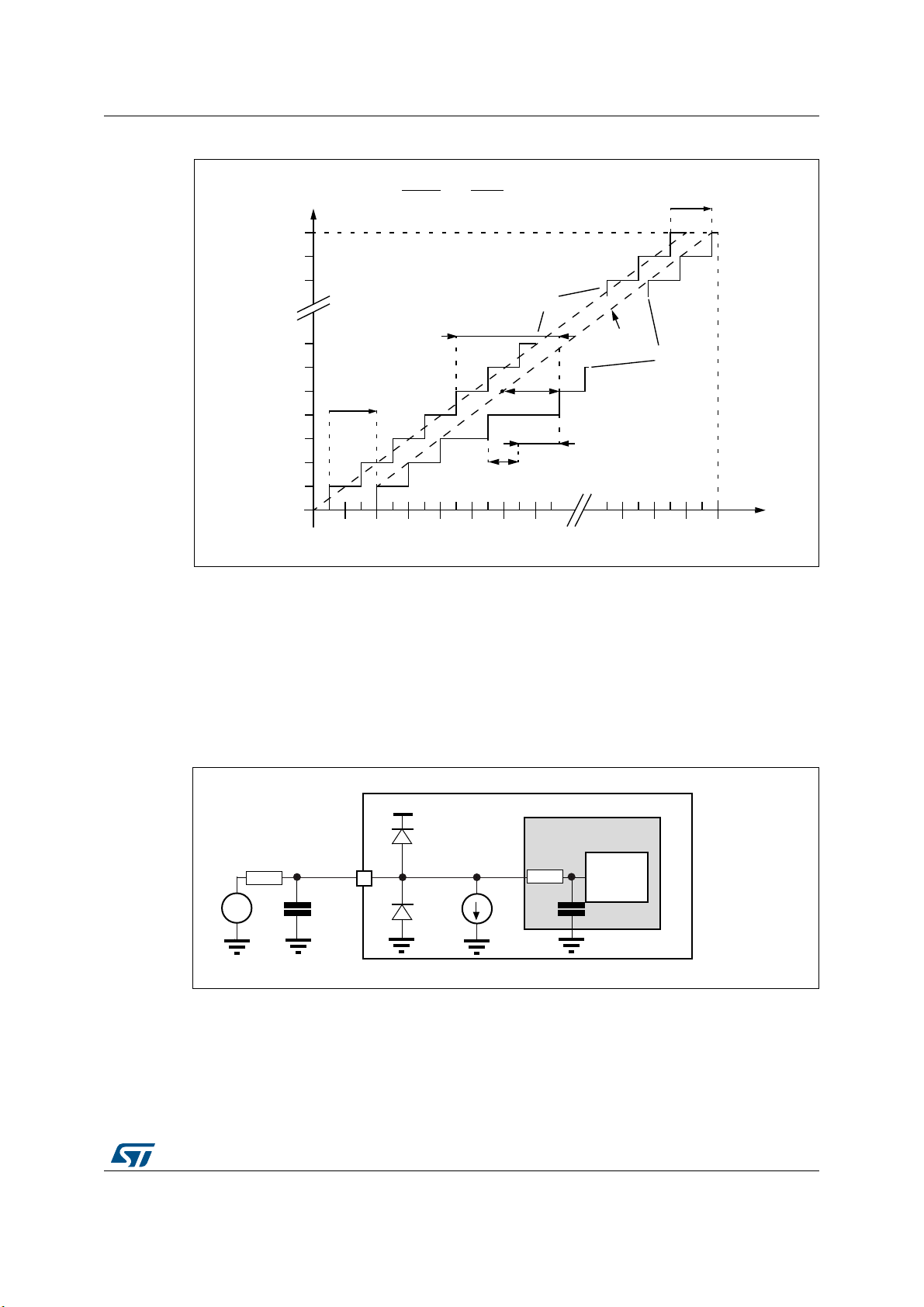

Figure 41. ADC accuracy characteristics

1. See also Table 64.

2. Example of an actual transfer curve.

3. Ideal transfer curve.

4. End point correlation line.

5. E

T

= Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves.

EO = Offset Error: deviation between the first actual transition and the first ideal one.

EG = Gain Error: deviation between the last ideal transition and the last actual one.

ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one.

EL = Integral Linearity Error: maximum deviation between any actual transition and the end point

correlation line.

Figure 42. Typical connection diagram using the ADC

1. Refer to Table 62 for the values of R

AIN

, R

ADC

and C

ADC

.

2. C

parasitic

represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the

pad capacitance (roughly 5 pF). A high C

parasitic

value downgrades conversion accuracy. To remedy this,

f

ADC

should be reduced.

AIC

%

/

%

'

, 3"

)$%!,

%

4

%

$

%

,

6

$$!

6

33!

6

2%&

ORDEPENDINGONPACKAGE=

6

$$!

;,3"

)$%!,

DL

670)

9

''

$,1[

,

/

$

9

9

7

5

$,1

&

SDUDVLWLF

9

$,1

9

9

7

5

$'&

&

$'&

ELW

FRQYHUWHU

6DPSOHDQGKROG$'&

FRQYHUWHU

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件