Datasheet 搜索 > 接口芯片 > Microchip(微芯) > USB3343-CP 数据手册 > USB3343-CP 数据手册 72/92 页

器件3D模型

器件3D模型¥ 10.413

USB3343-CP 数据手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

接口芯片

封装:

QFN-24

描述:

USB334x 系列 USB 2.0 收发器Microchip 的 USB334x 系列设备是高速 USB2.0 ULPI 收发器,支持 USB-IF 电池充电 1.2 (BC 1.2) 规格。### 特点符合 USB-IF 电池充电 1.2 规格 符合链路电源管理 (LPM) 规格 集成 ESD 保护电路 - 高达 ±25KV IEC 空气放电,无需外部设备 过压保护电路 (OVP) - 防止 VBUS 引脚受到电压高达 30V 的连续直流的损坏 集成 USB 开关 - 仅限 USB3341、USB3346 和 USB3347 型号 Microchip 的 RapidCharge Anywhere™: \- 通过 USB 端口的充电电流是传统解决方案的 3 倍 \- 符合 USB-IF 电池充电 1.2 规格,适用于任何便携式设备 \- 通过兼容 USB 主机或专用充电器的充电电流高达 1.5A \- 专用充电端口 (DCP)、充电 (CDP) 和标准 (SDP) 下游端口支持 flexPWR® 技术 - 极低电流设计,特别适用于电池供电应用 单电源操作 - 集成 1.8V 和 3.3V 调节器 PHYBoost - 可编程 USB 收发器驱动强度,用于还原信号完整性 VariSense™ - 可编程 USB 接收器灵敏度 免包装设计,用于优化定时性能和简化设计 提供外部参考时钟操作 智能检测电路允许识别 USB 充电器、耳机或数据电缆插入 包括对 On-The-Go 补充修订版 2.0 规格中详述的可选 On-The-Go (OTG) 协议的全面支持 支持 OTG 主机协商协议 (HNP) 和会话请求协议 (SRP) UART 模式,用于非 USB 串行数据传输 ID、DP 和 DM 线路至 VBUS 或接地连接内部 5V 电缆短路保护 ### USB (通用串行总线)- Microchip展开

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P11P12P13P14P15P16P65P66P67P69Hot

典型应用电路图在P2P42

原理图在P9P10P45P48

封装尺寸在P88

标记信息在P91

封装信息在P89P90

功能描述在P8

技术参数、封装参数在P17P20P27

应用领域在P1

电气规格在P19P24P25

导航目录

USB3343-CP数据手册

Page:

of 92 Go

若手册格式错乱,请下载阅览PDF原文件

Enhanced Single Supply Hi-Speed USB ULPI Transceiver

Datasheet

Revision 1.2 (02-08-13) 72 SMSC USB334x

DATASHEET

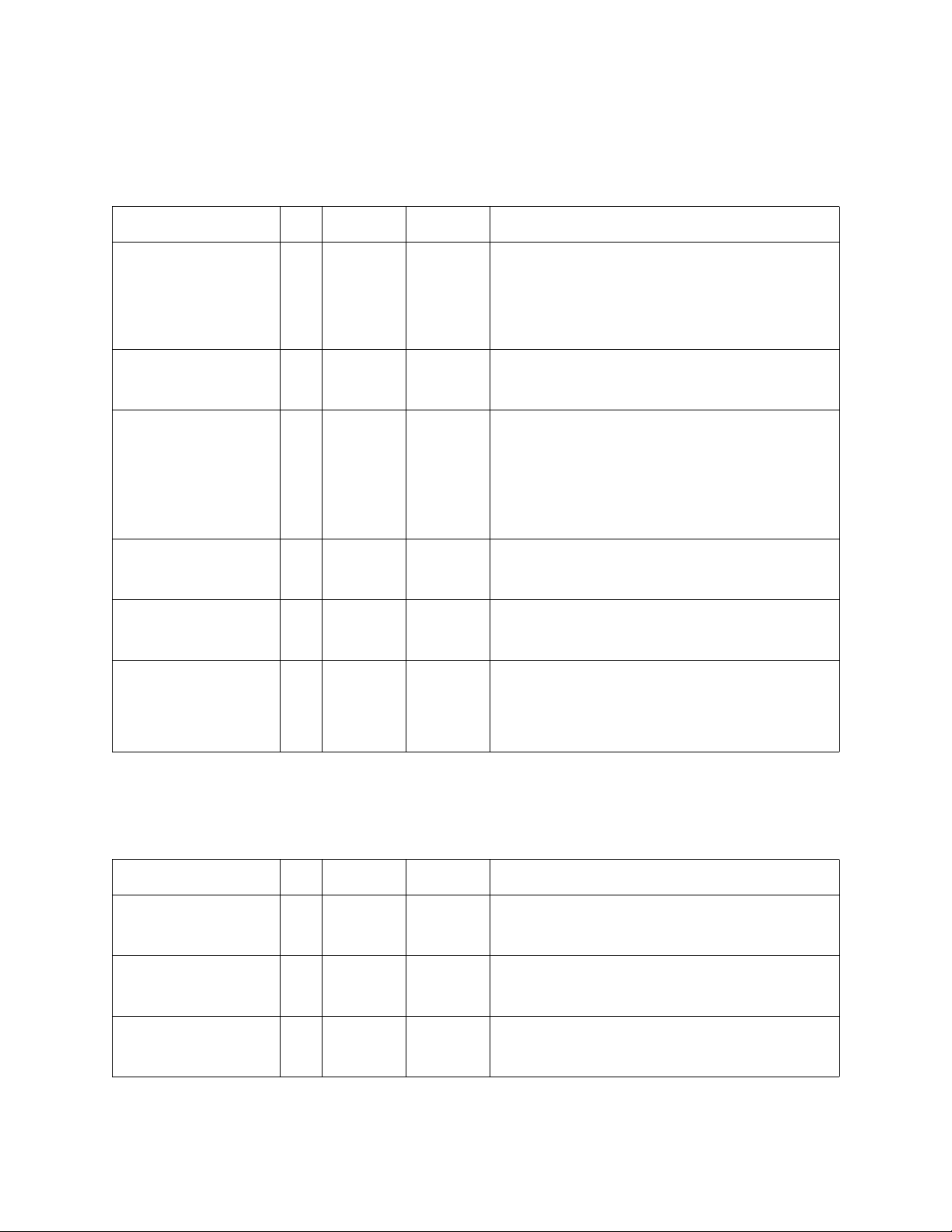

7.1.1.5 Function Control

Address = 04-06h (read), 04h (write), 05h (set), 06h (clear)

7.1.1.6 Interface Control

Address = 07-09h (read), 07h (write), 08h (set), 09h (clear)

FIELD NAME BIT ACCESS DEFAULT DESCRIPTION

XcvrSelect[1:0] 1:0 rd/w/s/c 01b Selects the required transceiver speed.

00b: Enables HS transceiver

01b: Enables FS transceiver

10b: Enables LS transceiver

11b: Enables FS transceiver for LS packets (FS

preamble automatically pre-pended)

TermSelect 2 rd/w/s/c 0b Controls the DP and DM termination depending on

XcvrSelect, OpMode, DpPulldown, and DmPulldown.

The DP and DM termination is detailed in Tab l e 5. 1 .

OpMode 4:3 rd/w/s/c 00b Selects the required bit encoding style during

transmit.

00b: Normal Operation

01b: Non-Driving

10b: Disable bit-stuff and NRZI encoding

11b: Reserved

Reset 5 rd/w/s/c 0b Active high transceiver reset. This reset does not

reset the ULPI interface or register set. Automatically

clears after reset is complete.

SuspendM 6 rd/w/s/c 1b Active low PHY suspend. When cleared the PHY will

enter Low Power Mode as detailed in 6.5.

Automatically set when exiting Low Power Mode.

LPM Enable 7 rd/w/s/c 0b When enabled the PLL start-up time is shortened to

allow fast start-up for LPM. The reduced PLL start-up

time is achieved by bypassing the VCO process

compensation which was done on initial start-up.

FIELD NAME BIT ACCESS DEFAULT DESCRIPTION

6-pin FsLsSerialMode 0 rd/w/s/c 0b When asserted the ULPI interface is redefined to the

6-pin Serial Mode. The PHY will automatically clear

this bit when exiting serial mode.

3-pin FsLsSerialMode 1 rd/w/s/c 0b When asserted the ULPI interface is redefined to the

3-pin Serial Mode. The PHY will automatically clear

this bit when exiting serial mode.

CarkitMode 2 rd/w/s/c 0b When asserted the ULPI interface is redefined to the

Carkit interface. The PHY will automatically clear this

bit when exiting Carkit Mode.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件