Datasheet 搜索 > FPGA芯片 > Altera(阿尔特拉) > 5SGXEA7N2F45C2LN 数据手册 > 5SGXEA7N2F45C2LN 产品描述及参数 2/20 页

¥ 65120.913

5SGXEA7N2F45C2LN 产品描述及参数 - Altera(阿尔特拉)

制造商:

Altera(阿尔特拉)

分类:

FPGA芯片

封装:

FBGA-1932

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

典型应用电路图在P3P4P6P7

封装尺寸在P8

导航目录

5SGXEA7N2F45C2LN数据手册

Page:

of 20 Go

若手册格式错乱,请下载阅览PDF原文件

Stratix V E devices offer the highest logic density within the Stratix V family with nearly one million logic

elements (LEs) in the largest device. These devices are optimized for applications such as ASIC and system

emulation, diagnostic imaging, and instrumentation.

Common to all Stratix V family variants are a rich set of high-performance building blocks, including a

redesigned adaptive logic module (ALM), 20 Kbit (M20K) embedded memory blocks, variable precision

DSP blocks, and fractional phase-locked loops (PLLs). All of these building blocks are interconnected by

Altera’s superior multi-track routing architecture and comprehensive fabric clocking network.

Also common to Stratix V devices is the new Embedded HardCopy Block, which is a customizable hard IP

block that leverages Altera’s unique HardCopy ASIC capabilities. The Embedded HardCopy Block in Stratix V

FPGAs is used to harden IP instantiation of PCIe Gen3, Gen2, and Gen1.

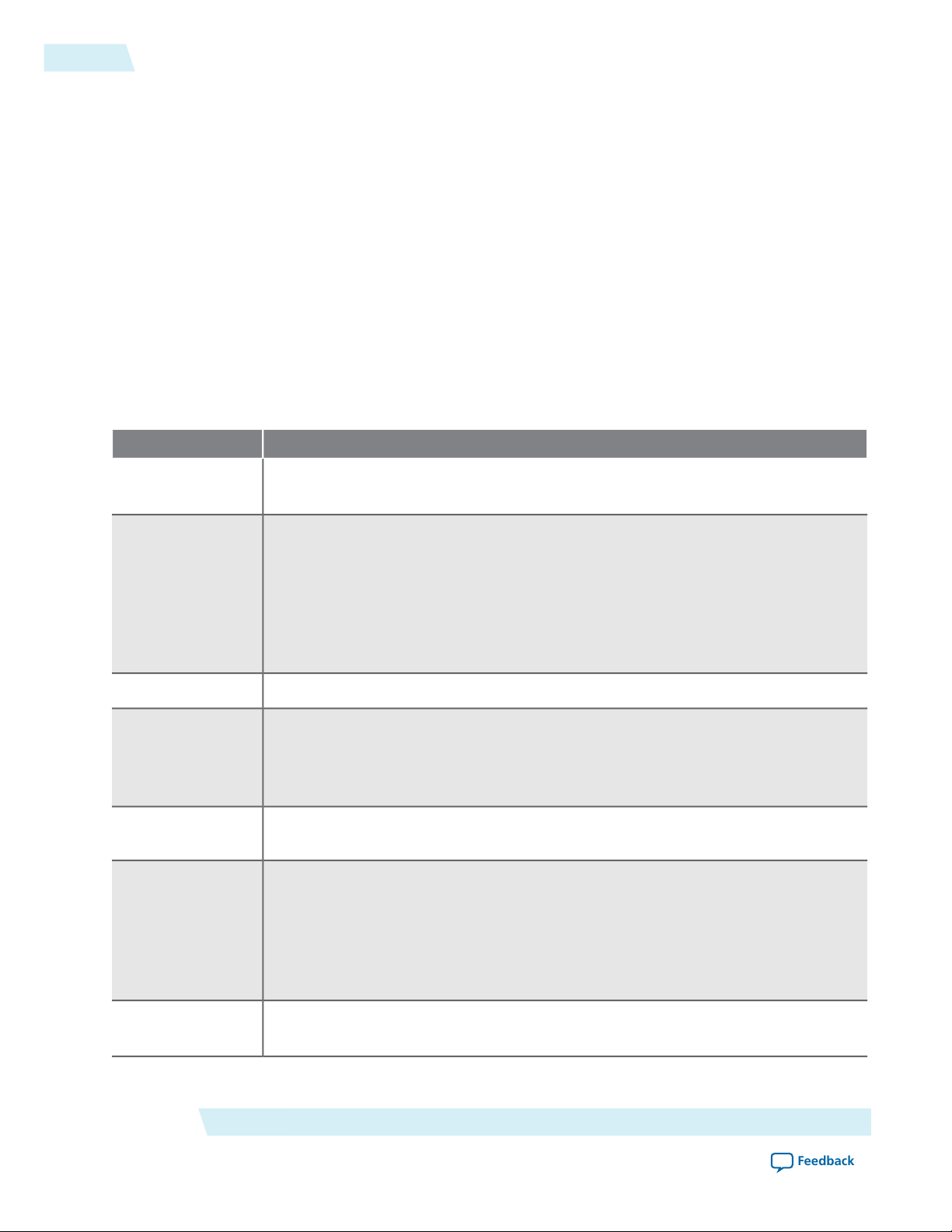

Stratix V Features Summary

Table 1: Summary of Features for Stratix V Devices

DescriptionFeature

• 28-nm TSMC process technology

• 0.85-V or 0.9-V core voltage

Technology

• 28.05-Gbps transceivers on Stratix V GT devices

• Electronic dispersion compensation (EDC) for XFP, SFP+, QSFP, CFP optical module

support

• Adaptive linear and decision feedback equalization

• Transmitter pre-emphasis and de-emphasis

• Dynamic reconfiguration of individual channels

• On-chip instrumentation (EyeQ non-intrusive data eye monitoring)

Low-power serial

transceivers

• 600-Megabits per second (Mbps) to 12.5-Gbps data rate capabilityBackplane capability

• 1.4-Gbps LVDS

• 1,066-MHz external memory interface

• On-chip termination (OCT)

• 1.2-V to 3.3-V interfacing for all Stratix V devices

General-purpose

I/Os (GPIOs)

• PCIe Gen3, Gen2, and Gen1 complete protocol stack, x1/x2/x4/x8 end point and root

port

Embedded

HardCopy Block

• Interlaken physical coding sublayer (PCS)

• Gigabit Ethernet (GbE) and XAUI PCS

• 10G Ethernet PCS

• Serial RapidIO

®

(SRIO) PCS

• Common Public Radio Interface (CPRI) PCS

• Gigabit Passive Optical Networking (GPON) PCS

Embedded

transceiver hard IP

• Programmable Power Technology

• Quartus II integrated PowerPlay Power Analysis

Power management

Stratix V Device Overview

Altera Corporation

Feedback

SV51001

Stratix V Features Summary

2

2013.05.06

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件