Datasheet 搜索 > 移位寄存器 > Diodes(美台) > 74AHCT595S16-13 数据手册 > 74AHCT595S16-13 其他数据使用手册 3/10 页

器件3D模型

器件3D模型¥ 1.066

74AHCT595S16-13 其他数据使用手册 - Diodes(美台)

制造商:

Diodes(美台)

分类:

移位寄存器

封装:

SOIC-16

描述:

74AHCT595S16-13 编带

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

74AHCT595S16-13数据手册

Page:

of 10 Go

若手册格式错乱,请下载阅览PDF原文件

74AHCT595

Document number: DS35487 Rev. 3 - 2

3 of 10

www.diodes.com

June 2013

© Diodes Incorporated

74AHCT595

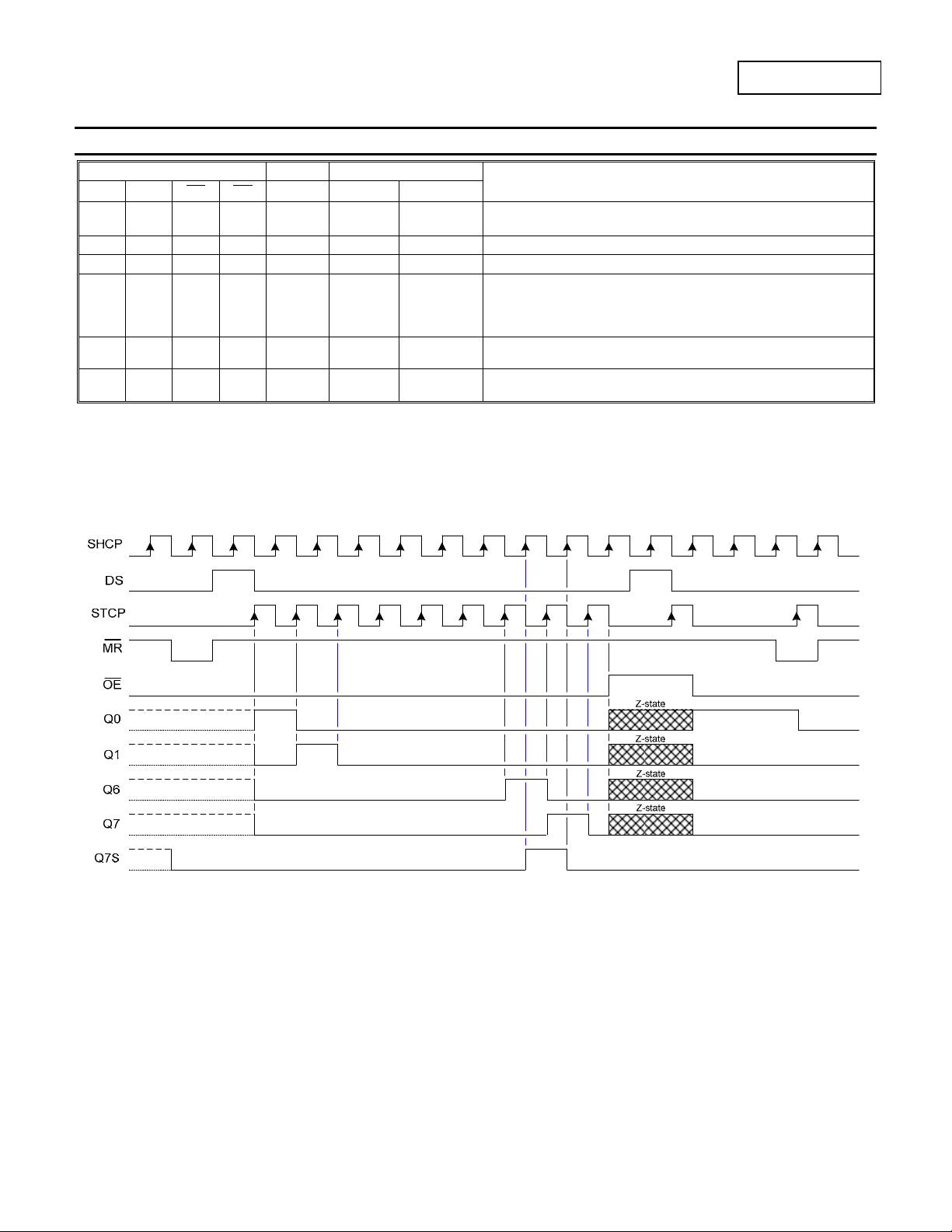

Functional Description and Timing Diagram

Control Input Output

Function

SHCP STCP OE MR DS Q7S Qn

X X L L

L NC

Low-level asserted on MR clears shift register.

Storage register is unchanged

X

L L

L L

Empty shift register transferred to storage register

X X H L

L Z

Shift register remains clear;: All Q ouputs in Z state.

X L H

Q6S NC

HIGH is shifted into first stage of Shift Register Contents of each

register shifted to next register

The content of Q6S has been shifted to Q7S and now appears on

device pin Q7S

X

L H

NC QnS

Contents of shift register copied to storage register. With output now

in active state the storage resister contents appear on Q outputs.

L H

Q6S QnS

Contents of shift register copied to output register then shift register

shifted.

H=HIGH voltage state

L=LOW voltage state

=LOW to HIGH transition

X= don’t care – high or low (not floating)

NC= No change

Z= high-impedance state

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件