Datasheet 搜索 > Integrated Device Technology(艾迪悌) > 9DML0451AKILFT 数据手册 > 9DML0451AKILFT 其他数据使用手册 1/13 页

¥ 0

9DML0451AKILFT 其他数据使用手册 - Integrated Device Technology(艾迪悌)

制造商:

Integrated Device Technology(艾迪悌)

封装:

VFQFN-24

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

9DML0451AKILFT数据手册

Page:

of 13 Go

若手册格式错乱,请下载阅览PDF原文件

DATASHEET

9DML04 REVISION A 06/06/16 1 ©2015 Integrated Device Technology, Inc.

2:4 3.3V PCIe Clock Mux 9DML04

Description

The 9DML04 devices are 3.3V members of IDT's

Full-Featured PCIe family. The 9DML04 supports PCIe

Gen1-4 Common Clocked (CC), Separate Reference no

Spread (SRnS), and Separate Reference Independent

Spread (SRIS) architectures. The part provides a choice of

asynchronous and glitch-free switching modes, and offers a

choice of integrated output terminations providing direct

connection to 85 or 100 transmission lines. The

9DML04P1 can be factory programmed with a user-defined

power up default SMBus configuration.

Recommended Application

Servers, ATCA, ATE, Master/Slave applications

Output Features

• 4 – 1~200 MHz Low-Power HCSL (LP-HCSL) DIF pairs

• 9DML0441 default ZOUT = 100

• 9DML0451 default ZOUT = 85

• 9DML04P1 factory programmable defaults

Key Specifications

• PCIe Gen1-2-3-4 CC compliant

• PCIe Gen2-3 SRIS compliant

• DIF additive cycle-to-cycle jitter <1ps

• DIF output-to-output skew <50ps

• Additive phase jitter is <0.1ps rms for PCIe

• Additive phase jitter 160fs rms typ. @156.25M (1.5M to

10M)

Features/Benefits

• Direct connection to 100 (xx41) or 85 (xx51)

transmission lines; saves 16 resistors compared to

standard PCIe devices

• 76mW typical power consumption; eliminates thermal

concerns

• Spread Spectrum (SS) compatible; allows SS for EMI

reduction

• Customer defined power up default can be factory

programmed into P1 device; allows exact optimization to

customer requirements:

• control input polarity

• control input pull up/downs

• slew rate for each output

• differential output amplitude

• output impedance for each output

• OE# pins; support DIF power management

• HCSL-compatible differential inputs; can be driven by

common clock source

• Selectable asynchronous or glitch-free switching; allows

the mux to be selected at power up even if both inputs are

not running, then transition to glitch-free switching mode

• Space saving 24-pin 4x4mm VFQFPN; minimal board

space

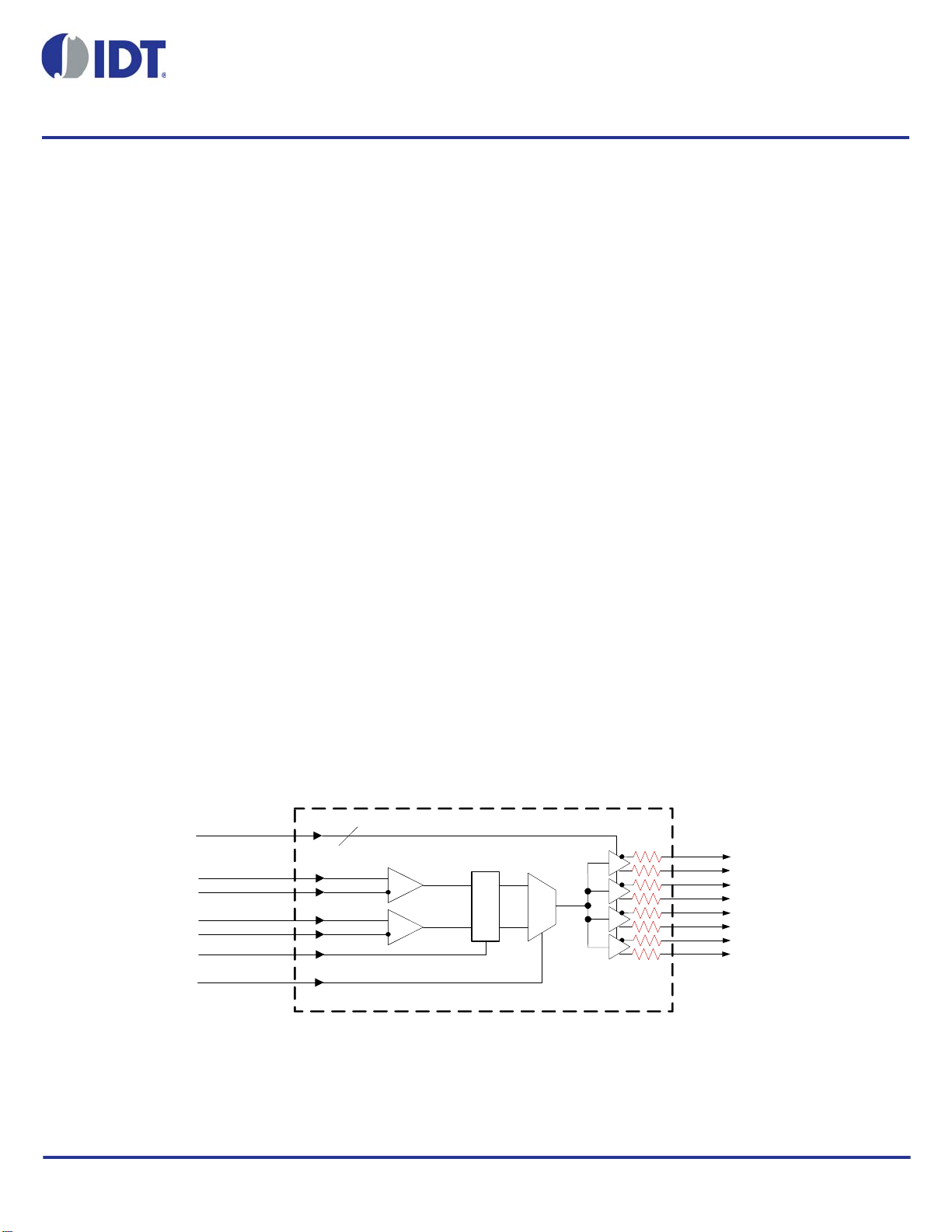

Block Diagram

Note: Resistors default to internal on 41/51 devices. P1 devices have programmable default impedances on an output-by-output basis.

DIF0

DIF1

DIF2

DIF3

A

B

4

^OE(3:0)#

DIF_INA

DIF_INB

vSW_MODE

^SEL_A_B#

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件