Datasheet 搜索 > 时钟信号器件 > ADI(亚德诺) > AD9548BCPZ-REEL7 数据手册 > AD9548BCPZ-REEL7 其他数据使用手册 1/112 页

器件3D模型

器件3D模型¥ 335.88

AD9548BCPZ-REEL7 其他数据使用手册 - ADI(亚德诺)

制造商:

ADI(亚德诺)

分类:

时钟信号器件

封装:

LFCSP-88

描述:

四路/八路输入网络时钟发生器/同步器 Quad/Octal Input Network Clock Generator/Synchronizer

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P15P33P51P112Hot

典型应用电路图在P46P51

原理图在P1P26P31P35P38P39P43

封装尺寸在P112

型号编码规则在P112

功能描述在P1P15P37P112

技术参数、封装参数在P1P4P8P10P11P14P107

应用领域在P1P37

电气规格在P18

导航目录

AD9548BCPZ-REEL7数据手册

Page:

of 112 Go

若手册格式错乱,请下载阅览PDF原文件

Quad/Octal Input Network Clock

Generator/Synchronizer

Data Sheet

AD9548

Rev. E Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2009–2013 Analog Devices, Inc. All rights reserved.

Technical Support www.analog.com

FEATURES

Supports Stratum 2 stability in holdover mode

Supports reference switchover with phase build-out

Supports hitless reference switchover

Auto/manual holdover and reference switchover

4 pairs of reference input pins with each pair configurable as

a single differential input or as 2 independent single-

ended inputs

Input reference frequencies from 1 Hz to 750 MHz

Reference validation and frequency monitoring (1 ppm)

Programmable input reference switchover priority

30-bit programmable input reference divider

4 pairs of clock output pins with each pair configurable as a

single differential LVDS/LVPECL output or as 2 single-

ended CMOS outputs

Output frequencies up to 450 MHz

30-bit integer and 10-bit fractional programmable feedback

divider

Programmable digital loop filter covering loop bandwidths

from 0.001 Hz to 100 kHz

Optional low noise LC-VCO system clock multiplier

Optional crystal resonator for system clock input

On-chip EEPROM to store multiple power-up profiles

Software controlled power-down

88-lead LFCSP package

APPLICATIONS

Network synchronization

Cleanup of reference clock jitter

GPS 1 pulse per second synchronization

SONET/SDH clocks up to OC-192, including FEC

Stratum 2 holdover, jitter cleanup, and phase transient

control

Stratum 3E and Stratum 3 reference clocks

Wireless base station controllers

Cable infrastructure

Data communications

GENERAL DESCRIPTION

The AD9548 provides synchronization for many systems,

including synchronous optical networks (SONET/SDH). The

AD9548 generates an output clock synchronized to one of up to

four differential or eight single-ended external input references.

The digital PLL allows for reduction of input time jitter or phase

noise associated with the external references. The AD9548

continuously generates a clean (low jitter), valid output clock

even when all references have failed by means of a digitally

controlled loop and holdover circuitry.

The AD9548 operates over an industrial temperature range of

−40°C to +85°C.

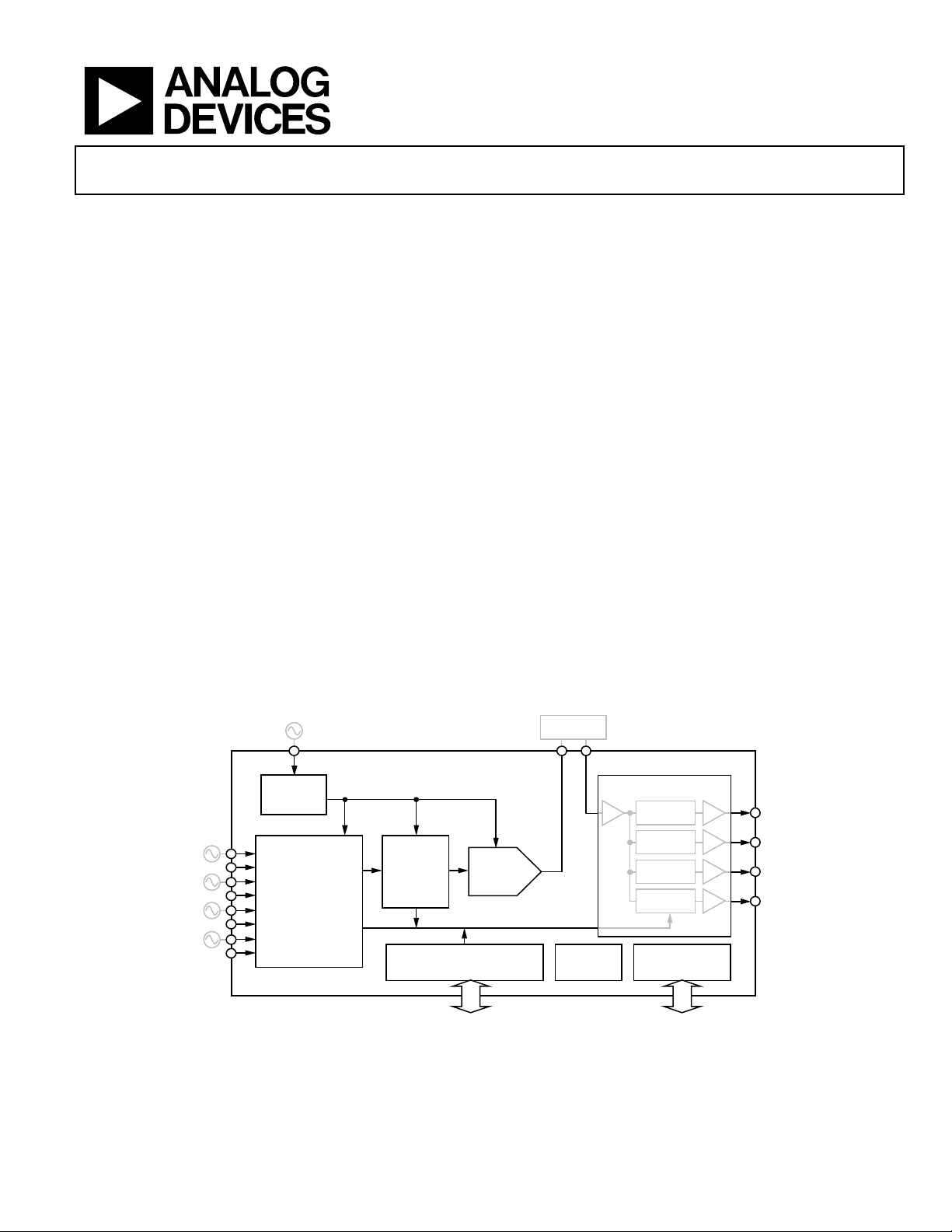

FUNCTIONAL BLOCK DIAGRAM

REFERENCE INPUTS

AND

MONITOR MUX

STATUS AND

CONTROL PINS

SERIAL CONTROL INTERFACE

(SPI or I

2

C)

EEPROM

DIGITAL

PLL

CLOCK DISTRIBUTION

SYNC

DAC

CLOCK

MULTIPLIER

STABLE

SOURCE

ANALOG

FILTER

AD9548

CHANNEL 0

DIVIDER

CHANNEL 1

DIVIDER

CHANNEL 2

DIVIDER

CHANNEL 3

DIVIDER

08022-001

Figure 1.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件