Datasheet 搜索 > EEPROM芯片 > Microchip(微芯) > 24LC01B-I/P 数据手册 > 24LC01B-I/P 产品设计参考手册 4/8 页

器件3D模型

器件3D模型¥ 1.477

24LC01B-I/P 产品设计参考手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

EEPROM芯片

封装:

PDIP-8

描述:

MICROCHIP 24LC01B-I/P EEPROM, AEC-Q100, 1 Kbit, 128 x 8位, 400 kHz, I2C, DIP, 8 引脚

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

型号编号列表在P3

导航目录

24LC01B-I/P数据手册

Page:

of 8 Go

若手册格式错乱,请下载阅览PDF原文件

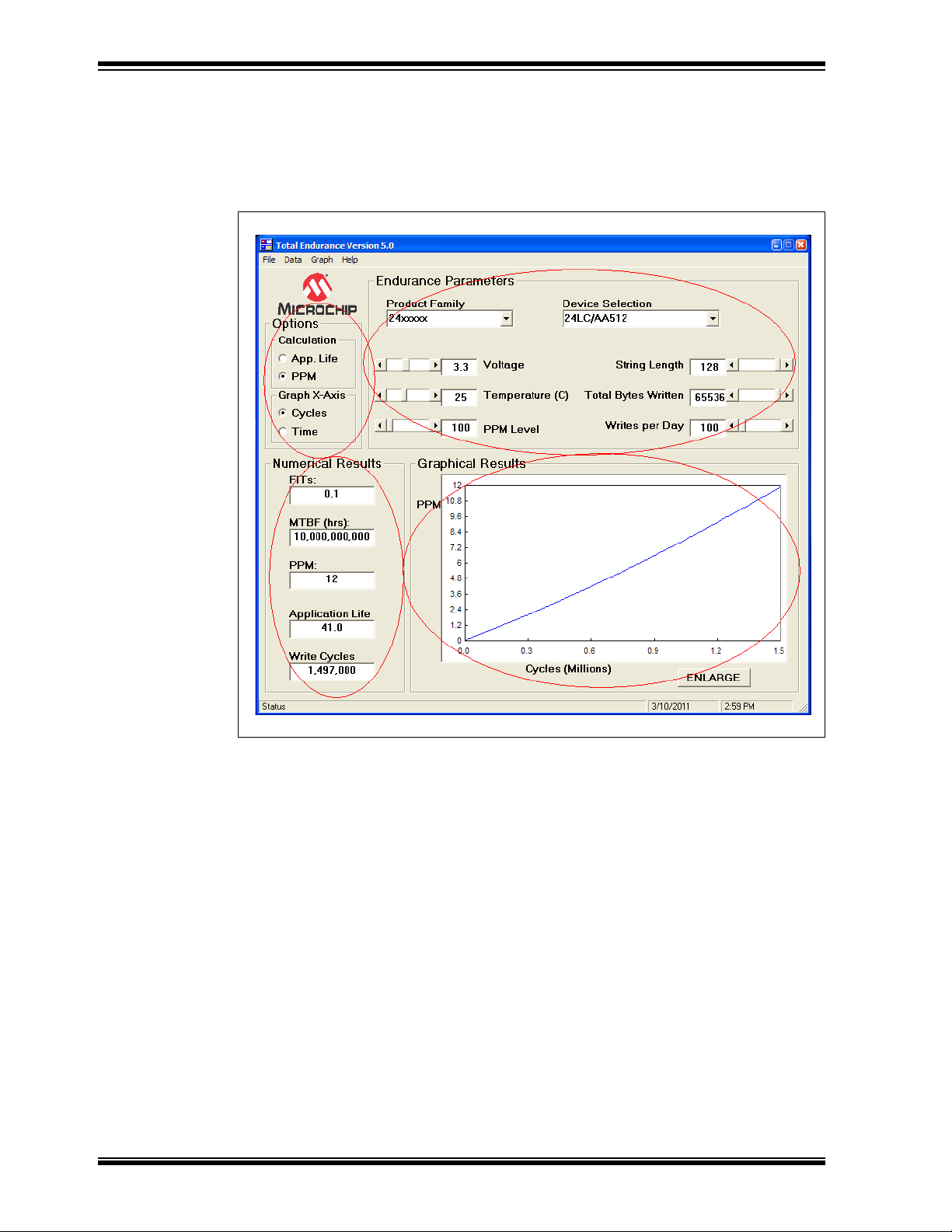

Total Endurance™ Quick Start Guide

DS51342B-page 4 © 2011 Microchip Technology Inc.

Graphic Results

This shows the failure rate over time (or cycles) up to the lifetime (calculated or entered)

of the application. The Enlarge button displays a full-screen version of the graph.

FAILURE RATE OVER TIME

ARCHITECTURE

Microchip employs two different array architectures in its EEPROM devices. The differ-

ence between the two involves what happens during the write cycle when less than a

full page is written. To the end user, this change does not affect communication; it only

affects how endurance is specified.

Byte Architecture

Microchip’s old EEPROM architecture was a byte architecture that allowed the user to

do a true byte write where only the byte(s) being addressed were modified during the

write cycle. The number of bytes being programmed in this architecture could be

anywhere from one single byte to an entire page.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件