Datasheet 搜索 > 时钟发生器 > Cypress Semiconductor(赛普拉斯) > CY25100SXCF 数据手册 > CY25100SXCF 用户编程技术手册 1/18 页

器件3D模型

器件3D模型¥ 2.542

CY25100SXCF 用户编程技术手册 - Cypress Semiconductor(赛普拉斯)

制造商:

Cypress Semiconductor(赛普拉斯)

分类:

时钟发生器

封装:

SOIC-8

描述:

CY25100 系列 单PLL 3.3 V 200 MHz 可编程 展频 时钟发生器 - SOIC-8

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

CY25100SXCF数据手册

Page:

of 18 Go

若手册格式错乱,请下载阅览PDF原文件

CY25100

Field and Factory Programmable Spread

Spectrum Clock Generator for EMI Reduction

Cypress Semiconductor Corporation • 198 Champion Court • San Jose, CA 95134-1709 • 408-943-2600

Document Number: 38-07499 Rev. *K Revised November 28, 2014

Field and Fa ctory Programmab le Spread Spectrum Clock Generator for EMI Redu ction

Features

■ Wide Operating Output (SSCLK) Frequency Range

❐ 3 MHz to 200 MHz

■ Programmable Spread Spectrum with nominal 31.5 kHz

Modulation Frequency

❐ Center Spread: ±0.25% to ±2.5%

❐ Down Spread: –0.5% to –5.0%

■ Input frequency range

❐ External Crystal: 8 to 30 MHz Fundamental Crystals

❐ External Reference: 8 to 166 MHz Clock

■ Integrated Phase-Locked Loop (PLL)

■ Field Programmable devices available

■ Programmable Crystal Load Capacitor Tuning Array

■ Low Cycle-to-cycle Jitter

■ Spread Spectrum on/off function

■ Powerdown or Output Enable function

■ Commercial and Industrial temperature ranges

■ 3.3 V operation

■ 8-pin TSSOP and SOIC packages

Functional Description

The CY25100 is a Spread Spectrum Clock Generator (SSCG) IC

used to reduce EMI found in today’s high speed digital electronic

systems.

The device uses a Cypress proprietary PLL and Spread

Spectrum Clock (SSC) technology to synthesize and modulate

the frequency of the input clock. By frequency modulating the

clock, the measured EMI at the fundamental and harmonic

frequencies are greatly reduced. This reduction in radiated

energy can significantly reduce the cost of complying with

regulatory agency (EMC) requirements and improve

time-to-market without degrading system performance.

The CY25100 uses a factory or field-programmable

configuration memory array to synthesize output frequency,

spread percentage, crystal load capacitor, reference clock output

on/off, spread spectrum on/off function, and PD#/OE options.

The spread percentage is programmed to either center spread

or down spread with various spread percentages. The range for

center spread is from ±0.25% to ±2.50%. The range for down

spread is from –0.5% to –5.0%.

The input to the CY25100 can either be a crystal or a clock

signal. The CY25100 has two clock outputs: REFCLK and

SSCLK. The non-spread spectrum REFCLK output has the

same frequency as the input of the CY25100.

For a complete list of related documentation, click here.

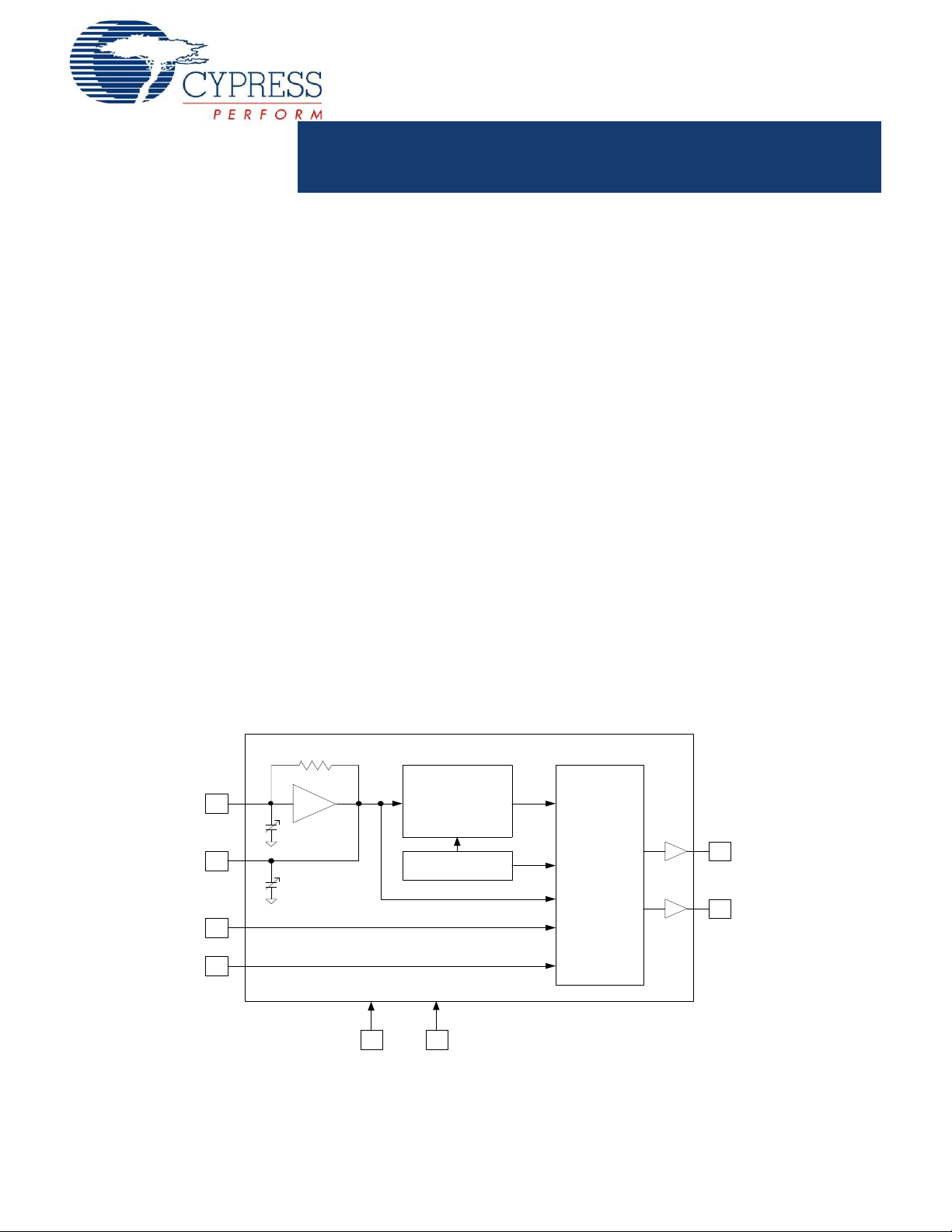

Logic Block Diagram

PLL

with

MODULATION

CONTROL

PROGRAMMABLE

CONFIGURATION

OUTPUT

DIVIDERS

and

MUX

3

2

4

8

1 5

7

6

VDD VSS

REFCLK

SSCLK

XOUT

XIN

PD# or OE

SSON#

RFB

C

XOUT

CXIN

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件