Datasheet 搜索 > Lattice Semiconductor(莱迪思) > GAL22V10C-10LJ 数据手册 > GAL22V10C-10LJ 用户编程技术手册 1/20 页

¥ 37.745

GAL22V10C-10LJ 用户编程技术手册 - Lattice Semiconductor(莱迪思)

制造商:

Lattice Semiconductor(莱迪思)

封装:

QCCJ

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

GAL22V10C-10LJ数据手册

Page:

of 20 Go

若手册格式错乱,请下载阅览PDF原文件

TIBPAL22V10C, TIBPAL22V10AC, TIBPAL22V10AM

HIGH-PERFORMANCE IMPACT™ PROGRAMMABLE ARRAY LOGIC CIRCUITS

SRPS024A − OCTOBER 1986 − REVISED APRIL 2010

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright © 2010, Texas Instruments Incorporated

1

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

• Second-Generation PLD Architecture

• Choice of Operating Speeds

TIBPAL22V10AC . . . 25 ns Max

TIBPAL22V10AM . . . 30 ns Max

TIBPAL22V10C . . . 35 ns Max

• Increased Logic Power − Up to 22 Inputs

and 10 Outputs

• Increased Product Terms − Average of 12

Per Output

• Variable Product Term Distribution

Allows More Complex Functions to Be

Implemented

• Each Output Is User Programmable for

Registered or Combinational Operation,

Polarity, and Output Enable Control

• TTL-Level Preload for Improved Testability

• Extra Terms Provide Logical Synchronous

Set and Asynchronous Reset Capability

• Fast Programming, High Programming

Yield, and Unsurpassed Reliability Ensured

Using Ti-W Fuses

• AC and DC Testing Done at the Factory

Utilizing Special Designed-In Test Features

• Dependable Texas Instruments Quality and

Reliability

• Package Options Include Both Plastic and

Ceramic Chip Carriers in Addition to Plastic

and Ceramic DIPs

• Functionally Equivalent to AMDs

AMPAL22V10 and AMPAL22V10A

description

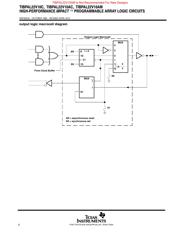

The TIBPAL22V10 and TIBPAL22V10A are programmable array logic devices featuring high speed and

functional equivalency when compared to presently available devices. They are implemented with the familiar

sum-of-products (AND-OR) logic structure featuring the new concept “Programmable Output Logic Macrocell”.

These IMPACT™ circuits combine the latest Advanced Low-Power Schottky technology with proven

titanium-tungsten fuses to provide reliable, high-performance substitutes for conventional TTL logic.

These devices contain up to 22 inputs and 10 outputs. They incorporate the unique capability of defining and

programming the architecture of each output on an individual basis. Outputs may be registered or nonregistered

and inverting or noninverting as shown in the output logic macrocell diagram. The ten potential outputs are

enabled through the use of individual product terms.

These devices are covered by U.S. Patent 4,410,987.

IMPACT is a trademark of Texas Instruments Incorporated.

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

CLK/I

I

I

I

I

I

I

I

I

I

I

GND

V

CC

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I

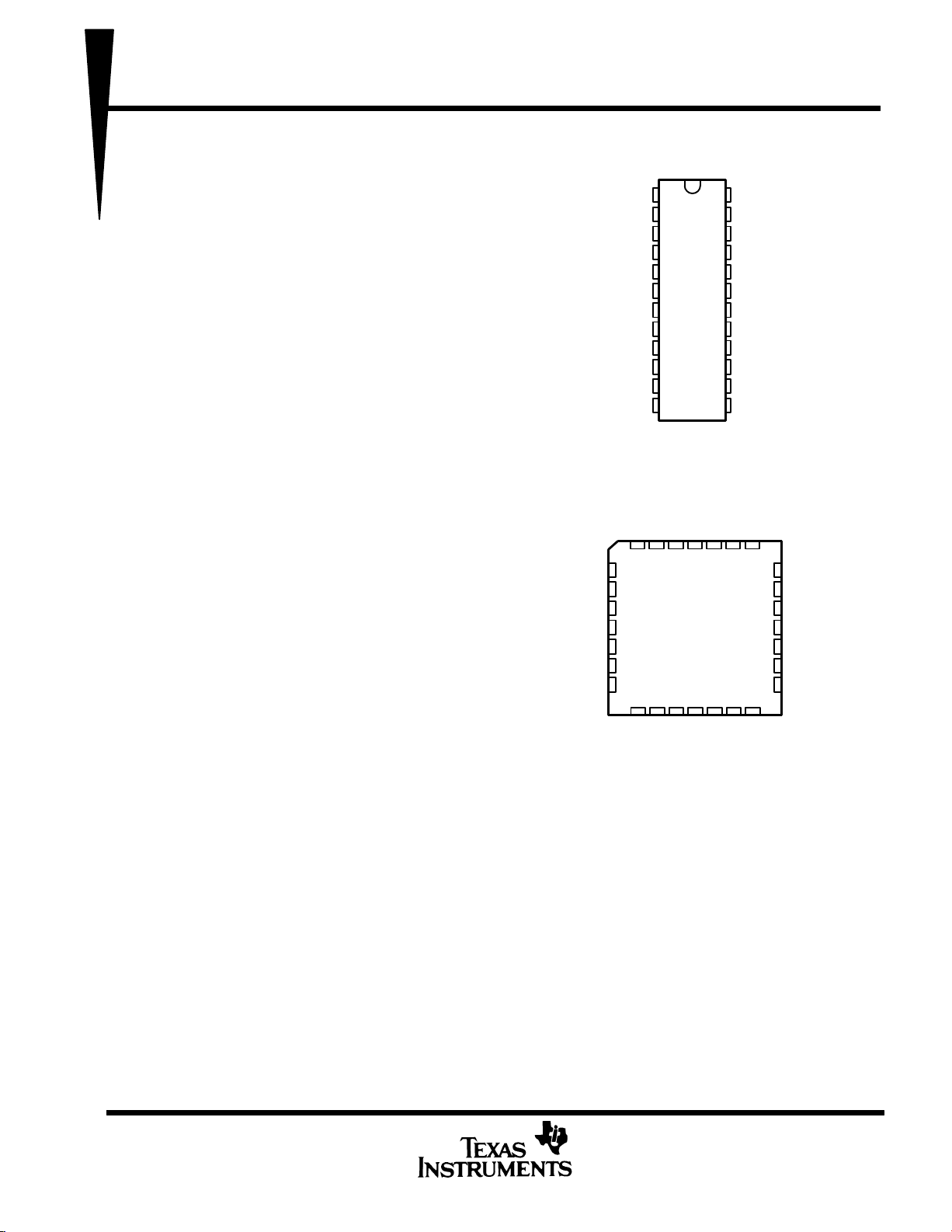

C SUFFIX . . . NT PACKAGE

M SUFFIX . . . JT OR W PACKAGE

(TOP VIEW)

3212827

12 13

5

6

7

8

9

10

11

25

24

23

22

21

20

19

I/O/Q

I/O/Q

I/O/Q

NC

I/O/Q

I/O/Q

I/O/Q

I

I

I

NC

I

I

I

426

14 15 16 17 18

I

I

GND

NC

I

I/O/Q

I/O/Q

I

I

CLK/I

NC

I/O/Q

I/O/Q

C SUFFIX . . . FN PACKAGE

M SUFFIX . . . FK PACKAGE

(TOP VIEW)

NC

− No internal connection

Pin assignments in operating mode

V

CC

TIBPAL22V10AM is Not Recommended For New Designs

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件