Datasheet 搜索 > DA转换器 > TI(德州仪器) > DAC1282IPWR 数据手册 > DAC1282IPWR 开发手册 3/12 页

器件3D模型

器件3D模型¥ 302.536

DAC1282IPWR 开发手册 - TI(德州仪器)

制造商:

TI(德州仪器)

分类:

DA转换器

封装:

TSSOP-24

描述:

低失真数位类比转换器用于地震 LOW DISTORTION DIGITAL-TO-ANALOG CONVERTER FOR SEISMIC

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

原理图在P1

导航目录

DAC1282IPWR数据手册

Page:

of 12 Go

若手册格式错乱,请下载阅览PDF原文件

Application Note AN-1282

ADUCM350 AS A LOW POWER DEVICE

The ADuCM350 is designed for use in low power, impedance

measurement applications. It features three low power mode

options: CORE_SLEEP, SYS_SLEEP, and hibernate.

CORE_SLEEP MODE

In CORE_SLEEP mode, the system gates the clock to the

Cortex-M3 processor after it enters sleep mode. The rest of the

system remains active. No instructions can be executed; however,

direct memory access (DMA) transfers can continue to happen

between peripherals and memories.

This mode has the advantage of eliminating instruction accesses

to flash memory, as well as usage of stack and temporary

variables in SRAM0, significantly reducing dynamic power in

the system. DMA accesses into SRAM or flash automatically

enable the clocks to that particular block. The nested vector

interrupt controller (NVIC) clock, FCLK, remains active, and

the NVIC processes the wake-up events.

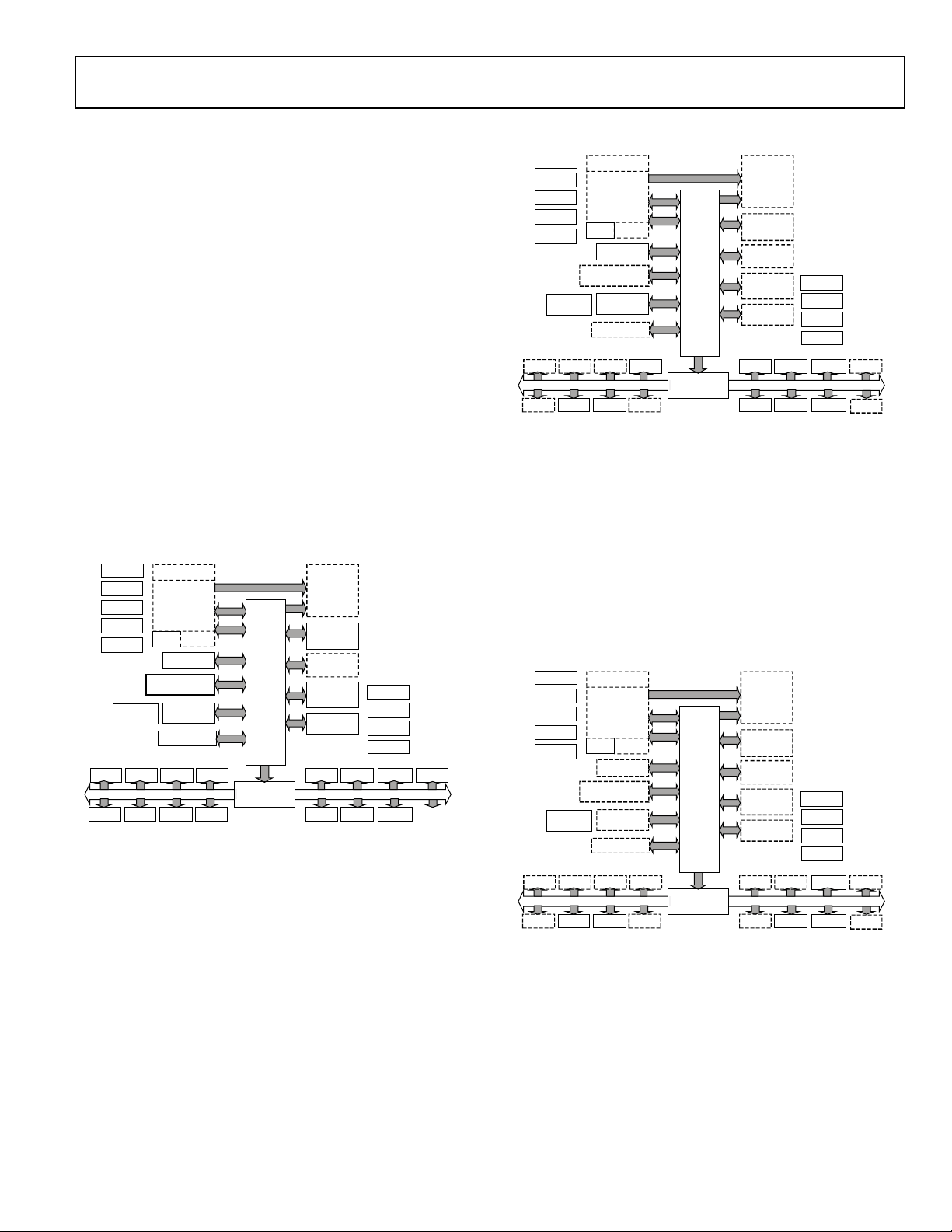

Figure 2 shows the ADuCM350 in the default CORE_SLEEP

mode with only the core clock gated. Figure 3 shows an example

where various submodules are also clock gated in CORE_SLEEP

mode to provide additional power reduction.

Figure 2. CORE_SLEEP Mode (Default)

Figure 3. CORE_SLEEP Mode with Some Modules Clock Gated

SYS_SLEEP MODE

In SYS_SLEEP mode, the system gates the system bus clock

(HCLK) and peripheral bus clock (PCLK) after the Cortex-M3

processor enters sleep mode. The gating of these clocks stops all

advanced high performance bus (AHB) attached masters/slaves

and all peripherals attached to the advanced peripheral bus

(APB). Peripheral clocks are all off, and they are no longer user

programmable. The NVIC clock (FCLK) remains active, and

the NVIC processes the wake-up events.

Figure 4 shows SYS_SLEEP mode, where the majority of the

ADuCM350 modules are clock gated.

Figure 4. SYS_SLEEP Mode

PLL

1 × 256kB

1 × 128kB

FLASH

PDI

SW/JTAG

CORTEX -

M3

NVIC

TRACE

LF XTAL

HF XTAL

HF OSC

LF OSC

USB PHY

DMA

AFE

CONTROLLER

USB

CAP TOUCH

AHB-APB

BRIDGE

UART

I

2

S

SPI0

LCD

SPI1

GPIO

I

2

C

CRC

TMR0

TMR2

TMR1

WDT

PMU

RTC

BEEP

MISC

16kB

EEPROM

SRAM0

(16kB)

HP LDO

POR

LP LDO

PSM

SRAM1

(16kB)

12007-002

APB-0 APB-1

AMBA

BUS

MATRIX

PLL

1 × 256kB

1 × 128kB

FLASH

PDI

SW/JTAG

CORTEX -

M3

NVIC

TRACE

LF XTAL

HF XTAL

HF OSC

LF OSC

USB PHY

DMA

AFE

CONTROLLER

USB

CAP TOUCH

AHB-APB

BRIDGE

UART

I

2

S

SPI0

LCD

SPI1

GPIO

I

2

C

CRC

TMR0

TMR2

TMR1

WDT

PMU

RTC

BEEP

MISC

16kB

EEPROM

SRAM0

(16kB)

HP LDO

POR

LP LDO

PSM

SRAM1

(16kB)

12007-003

APB-0 APB-1

AMBA

BUS

MATRIX

PLL

1 × 256kB

1 × 128kB

FLASH

PDI

SW/JTAG

CORTEX -

M3

NVIC

TRACE

LF XTAL

HF XTAL

HF OSC

LF OSC

USB PHY

DMA

AFE

CONTROLLER

USB

CAP TOUCH

AHB-APB

BRIDGE

UART

I

2

S

SPI0

LCD

SPI1

GPIO

I

2

C

CRC

TMR0

TMR2

TMR1

WDT

PMU

RTC

BEEP

MISC

16kB

EEPROM

SRAM0

(16kB)

HP LDO

POR

LP LDO

PSM

SRAM1

(16kB)

12007-004

APB-0 APB-1

AMBA

BUS

MATRIX

Rev. 0 | Page 3 of 12

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件