Datasheet 搜索 > 振荡器 > Silicon Labs(芯科) > 510BBA100M000AAG 数据手册 > 510BBA100M000AAG 数据手册 6/26 页

¥ 8.746

510BBA100M000AAG 数据手册 - Silicon Labs(芯科)

制造商:

Silicon Labs(芯科)

分类:

振荡器

封装:

SMD-6

描述:

SILICON LABS 510BBA100M000AAG 振荡器, 100MHZ, ±50PPM, 3.3V, SMD

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P1P12Hot

典型应用电路图在P26

原理图在P1

封装尺寸在P10P16P18P20P22

型号编码规则在P1P14

封装信息在P14

技术参数、封装参数在P4P11P24

应用领域在P1

电气规格在P4

型号编号列表在P24

导航目录

510BBA100M000AAG数据手册

Page:

of 26 Go

若手册格式错乱,请下载阅览PDF原文件

Si510/511

6 Rev. 1.2

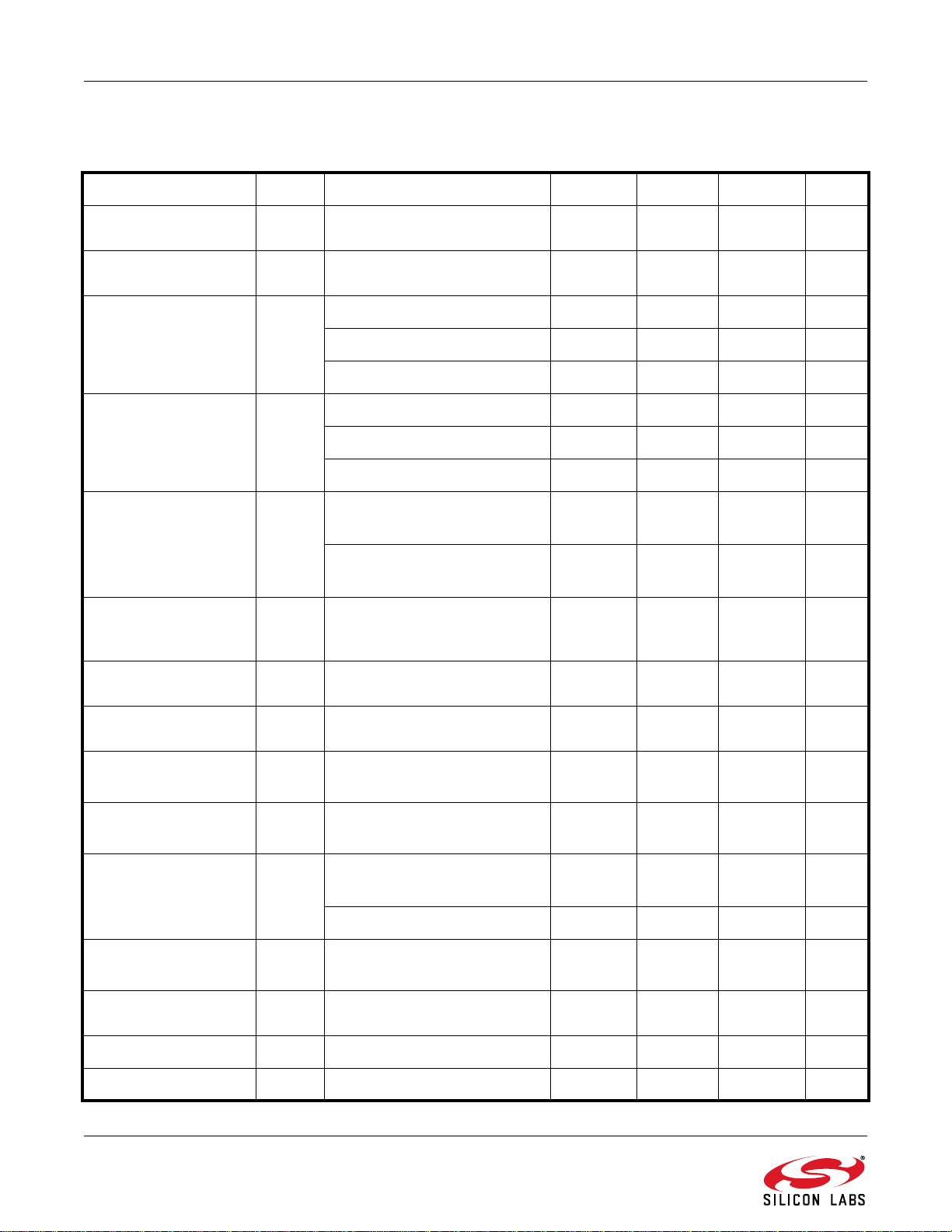

Table 3. Output Clock Levels and Symmetry

V

DD

= 1.8 V ±5%, 2.5 or 3.3 V ±10%, T

A

= –40 to +85

o

C

Parameter Symbol Test Condition Min Typ Max Unit

CMOS Output Logic

High

V

OH

0.85 x V

DD

——V

CMOS Output Logic

Low

V

OL

— — 0.15 x V

DD

V

CMOS Output Logic

High Drive

I

OH

3.3 V –8 — — mA

2.5 V –6 — — mA

1.8 V –4 — — mA

CMOS Output Logic

Low Drive

I

OL

3.3 V 8 — — mA

2.5 V 6 — — mA

1.8 V 4 — — mA

CMOS Output Rise/Fall

Time

(20 to 80% V

DD

)

T

R

/T

F

0.1 to 212.5 MHz,

C

L

= 15 pF

0.45 0.8 1.2 ns

0.1 to 212.5 MHz,

C

L

= no load

0.3 0.6 0.9 ns

LVPECL Output

Rise/Fall Time

(20 to 80% VDD)

T

R

/T

F

100 — 565 ps

HCSL Output Rise/Fall

Time (20 to 80% VDD)

T

R

/T

F

100 — 470 ps

LVDS Output Rise/Fall

Time (20 to 80% VDD)

T

R

/T

F

350 — 800 ps

LVPECL Output

Common Mode

V

OC

50 to V

DD

– 2 V,

single-ended

—V

DD

–

1.4 V

—V

LVPECL Output Swing

V

O

50 to V

DD

– 2 V,

single-ended

0.55 0.8 0.90 V

PPSE

LVDS Output Common

Mode

V

OC

100 line-line

V

DD

= 3.3/2.5 V

1.13 1.23 1.33 V

100 line-line, V

DD

= 1.8 V 0.83 0.92 1.00 V

LVDS Output Swing

V

O

Single-ended, 100 differential

termination

0.25 0.35 0.45 V

PPSE

HCSL Output Common

Mode

V

OC

50 to ground 0.35 0.38 0.42 V

HCSL Output Swing

V

O

Single-ended 0.58 0.73 0.85 V

PPSE

Duty Cycle

DC All formats 485052%

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件