Datasheet 搜索 > FPGA芯片 > Altera(阿尔特拉) > 5CSEBA2U23C8SN 数据手册 > 5CSEBA2U23C8SN 数据手册 16/96 页

¥ 192.392

5CSEBA2U23C8SN 数据手册 - Altera(阿尔特拉)

制造商:

Altera(阿尔特拉)

分类:

FPGA芯片

封装:

UBGA-672

描述:

FPGA - 现场可编程门阵列 CycloneV SoC SE SNGL -core ARM Cortex-A9

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P16Hot

技术参数、封装参数在P1P2P11P12P13P15P16P18P19P22P23P24

电气规格在P1

导航目录

5CSEBA2U23C8SN数据手册

Page:

of 96 Go

若手册格式错乱,请下载阅览PDF原文件

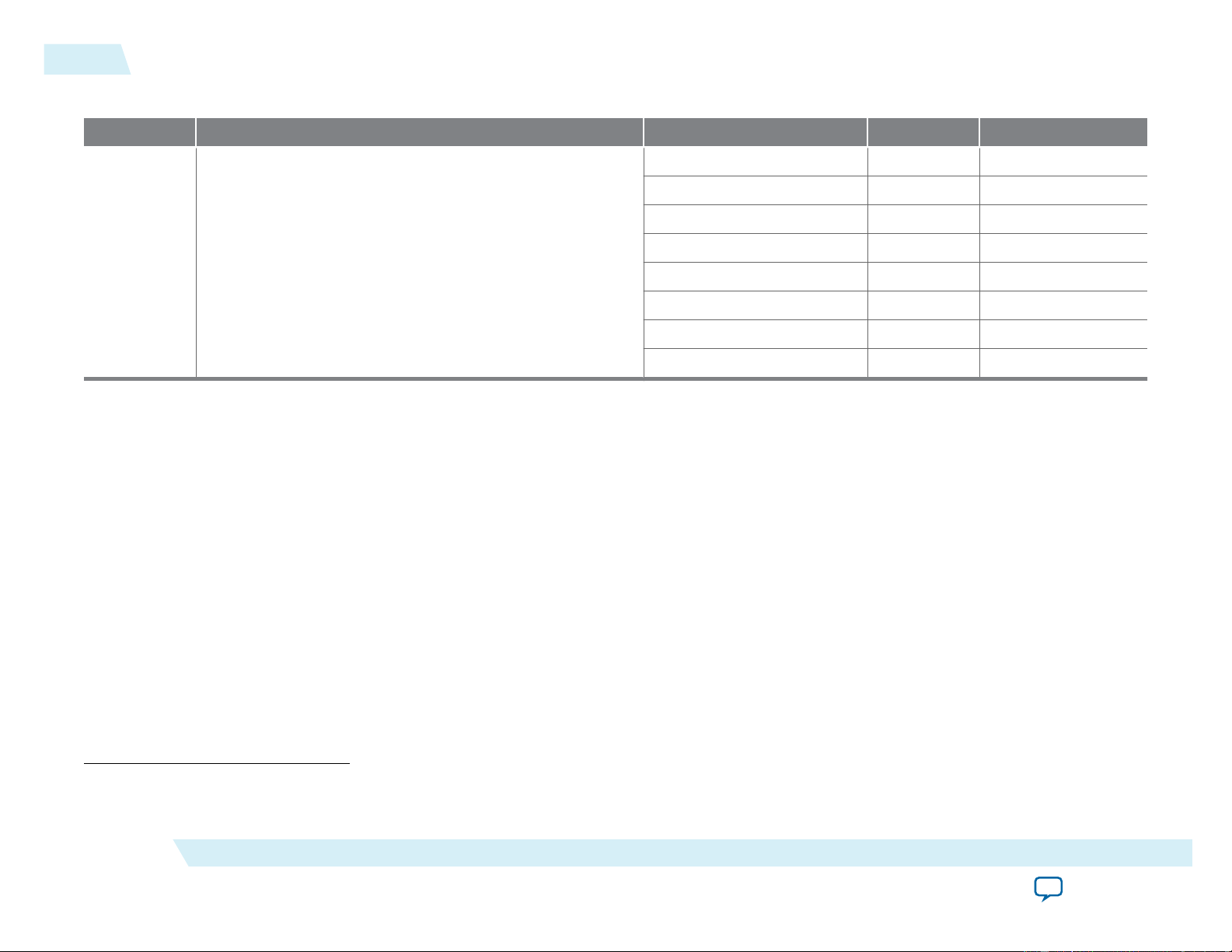

Table 13: Internal Weak Pull-Up Resistor Values for Devices

Symbol Description Condition (V)

(16)

Value

(17)

Unit

R

PU

Value of the I/O pin pull-up resistor before and during

configuration, as well as user mode if you have enabled the

programmable pull-up resistor option.

V

CCIO

= 3.3 ±5% 25 kΩ

V

CCIO

= 3.0 ±5% 25 kΩ

V

CCIO

= 2.5 ±5% 25 kΩ

V

CCIO

= 1.8 ±5% 25 kΩ

V

CCIO

= 1.5 ±5% 25 kΩ

V

CCIO

= 1.35 ±5% 25 kΩ

V

CCIO

= 1.25 ±5% 25 kΩ

V

CCIO

= 1.2 ±5% 25 kΩ

Related Information

Cyclone V Device Family Pin Connection Guidelines

Provides more information about the pins that support internal weak pull-up and internal weak pull-down features.

I/O Standard Specifications

Tables in this section list the input voltage (V

IH

and V

IL

), output voltage (V

OH

and V

OL

), and current drive characteristics (I

OH

and I

OL

) for various

I/O standards supported by devices.

You must perform timing closure analysis to determine the maximum achievable frequency for general purpose I/O standards.

(16)

Pin pull-up resistance values may be lower if an external source drives the pin higher than V

CCIO

.

(17)

Valid with ±10% tolerances to cover changes over PVT.

16

I/O Standard Specifications

CV-51002

2016.06.10

Altera Corporation

Cyclone V Device Datasheet

Send Feedback

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件