Datasheet 搜索 > 逻辑控制器 > Nexperia(安世) > 74AHCT595PW,112 数据手册 > 74AHCT595PW,112 数据手册 6/23 页

器件3D模型

器件3D模型¥ 0.312

74AHCT595PW,112 数据手册 - Nexperia(安世)

制造商:

Nexperia(安世)

分类:

逻辑控制器

封装:

TSSOP-16

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

74AHCT595PW,112数据手册

Page:

of 23 Go

若手册格式错乱,请下载阅览PDF原文件

74AHC_AHCT595 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 5 — 4 July 2012 5 of 22

NXP Semiconductors

74AHC595; 74AHCT595

8-bit serial-in/serial-out or parallel-out shift register with output latches

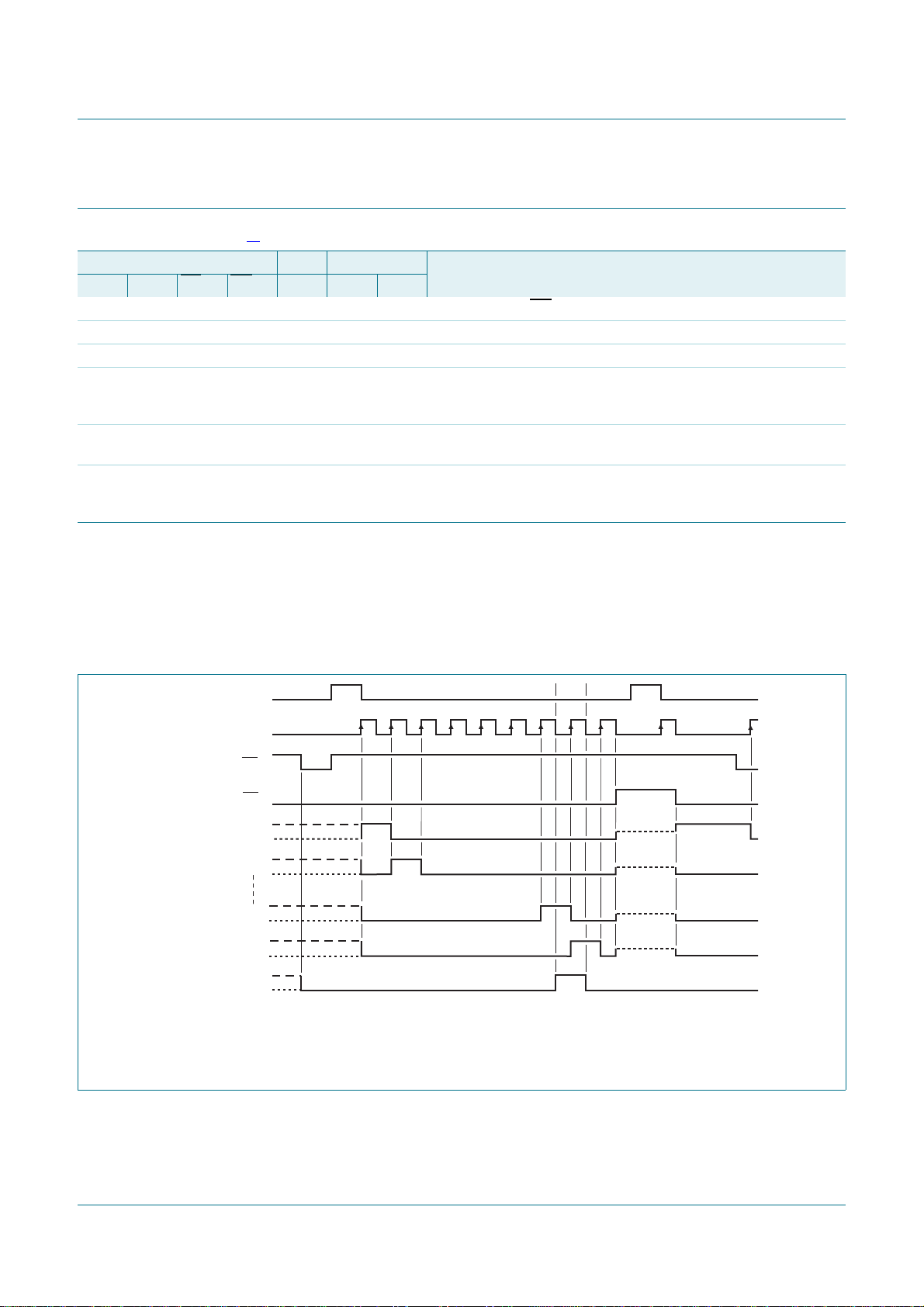

7. Functional description

[1] H = HIGH voltage state;

L = LOW voltage state;

= LOW-to-HIGH transition;

X = don’t care;

NC = no change;

Z = high-impedance OFF-state.

Table 3. Function table

[1]

Control Input Output Function

SHCP STCP OE MR DS Q7S Qn

X X L L X L NC a LOW-level on MR

only affects the shift registers

X L L X L L empty shift register loaded into storage register

X X H L X L Z shift register clear; parallel outputs in high-impedance OFF-state

X L H H Q6S NC logic HIGH-level shifted into shift register stage 0. Contents of all

shift register stages shifted through, e.g. previous state of stage 6

(internal Q6S) appears on the serial output (Q7S).

X L H X NC QnS contents of shift register stages (internal QnS) are transferred to

the storage register and parallel output stages

L H X Q6S QnS contents of shift register shifted through; previous contents of the

shift register is transferred to the storage register and the parallel

output stages

Fig 7. Timing diagram

DS

STCP

MR

OE

Q0

Q1

Q6

Q7

Q7S

Z-state

Z-state

Z-state

Z-state

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件