Datasheet 搜索 > 锁存器 > Integrated Device Technology(艾迪悌) > 74LVC16373APAG 数据手册 > 74LVC16373APAG 数据手册 1/7 页

器件3D模型

器件3D模型¥ 2.898

74LVC16373APAG 数据手册 - Integrated Device Technology(艾迪悌)

制造商:

Integrated Device Technology(艾迪悌)

分类:

锁存器

封装:

TSSOP-48

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

74LVC16373APAG数据手册

Page:

of 7 Go

若手册格式错乱,请下载阅览PDF原文件

INDUSTRIAL TEMPERATURE RANGE

IDT74LVC16373A

3.3V CMOS 16-BIT TRANSPARENT D-TYPE LATCH

1

JULY 2015INDUSTRIAL TEMPERATURE RANGE

IDT and the IDT logo is a registered trademark of Integrated Device Technology, Inc.

© 2015 Integrated Device Technology, Inc. DSC-4624/6

FEATURES:

• Typical tSK(o) (Output Skew) < 250ps

• ESD > 2000V per MIL-STD-883, Method 3015; > 200V using

machine model (C = 200pF, R = 0)

•VCC = 3.3V ± 0.3V, Normal Range

•VCC = 2.7V to 3.6V, Extended Range

• CMOS power levels (0.4

μμ

μμ

μ W typ. static)

• All inputs, outputs, and I/O are 5V tolerant

• Supports hot insertion

• Available in SSOP and TSSOP packages

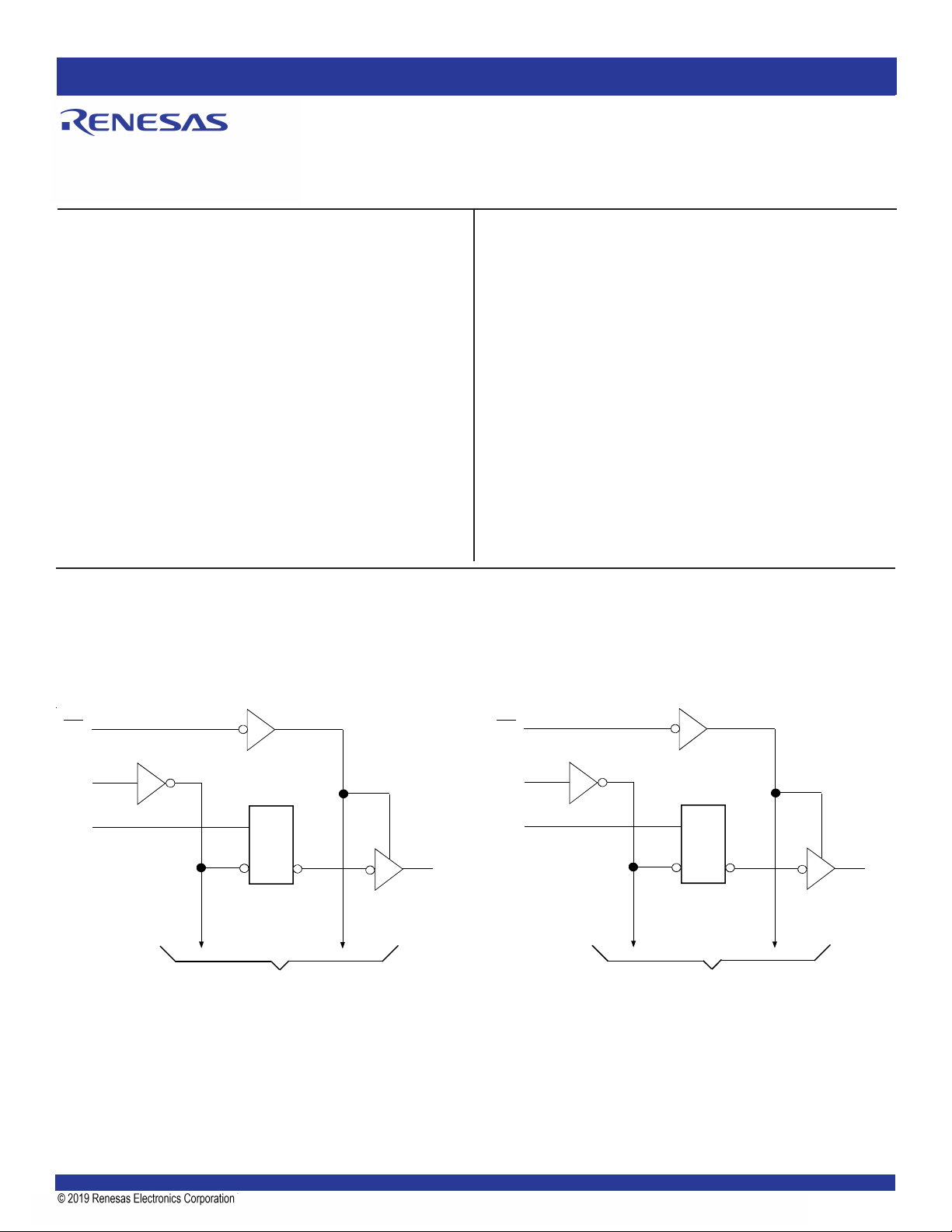

FUNCTIONAL BLOCK DIAGRAM

APPLICATIONS:

• 5V and 3.3V mixed voltage systems

• Data communication and telecommunication systems

DRIVE FEATURES:

• High Output Drivers: ±24mA

• Reduced system switching noise

IDT74LVC16373A

DESCRIPTION:

The LVC16373A 16-bit transparent D-type latch is built using advanced

dual metal CMOS technology. This high-speed, low-power latch is ideal

for temporary storage of data. The LVC16373A can be used for implement-

ing memory address latches, I/O ports, and bus drivers. The Output Enable

and Latch Enable controls are organized to operate each device as two 8-

bit latches or one 16-bit latch. Flow-through organization of signal pins

simplifies layout. All inputs are designed with hysteresis for improved noise

margin.

All pins of the LVC16373A can be driven from either 3.3V or 5V devices.

This feature allows the use of this device as a translator in a mixed 3.3V/

5V supply system.

The LVC16373A has been designed with a ±24mA output driver. This

driver is capable of driving a moderate to heavy load while maintaining

speed performance.

1OE

D

C

1LE

1D1

1

Q1

TO SEVEN OTHER CHANNELS

2OE

D

C

2LE

2D1

2

Q1

1

48

47

24

25

36

2

13

Q

Q

TO SEVEN OTHER CHANNELS

3.3V CMOS 16-BIT

TRANSPARENT D-TYPE

LATCH WITH 3-STATE OUTPUTS

AND 5 VOLT TOLERANT I/O

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件