Datasheet 搜索 > 锁存器 > Integrated Device Technology(艾迪悌) > 74LVC16373APAG 数据手册 > 74LVC16373APAG 数据手册 5/7 页

器件3D模型

器件3D模型¥ 2.898

74LVC16373APAG 数据手册 - Integrated Device Technology(艾迪悌)

制造商:

Integrated Device Technology(艾迪悌)

分类:

锁存器

封装:

TSSOP-48

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

74LVC16373APAG数据手册

Page:

of 7 Go

若手册格式错乱,请下载阅览PDF原文件

INDUSTRIAL TEMPERATURE RANGE

IDT74LVC16373A

3.3V CMOS 16-BIT TRANSPARENT D-TYPE LATCH

5

Open

VLOAD

GND

VCC

Pulse

Generator

D.U.T.

500

500

CL

RT

VIN

VOUT

(1, 2)

LVC Link

INPUT

VIH

0V

V

OH

VOL

tPLH1

tSK (x)

OUTPUT 1

OUTPUT 2

t

PHL1

tSK (x)

tPLH2

tPHL2

VT

VT

VOH

VT

VOL

tSK(x) = tPLH2 - tPLH1 or tPHL2 - tPHL1

LVC Link

SAME PHASE

INPUT TRANSITION

OPPOSITE PHASE

INPUT TRANSITION

0V

0V

V

OH

VOL

tPLH

tPHL

tPHL

tPLH

OUTPUT

VIH

VT

VT

VIH

VT

LVC Link

DATA

INPUT

0V

0V

0V

0V

tREM

TIMING

INPUT

ASYNCHRONOUS

CONTROL

SYNCHRONOUS

CONTROL

t

SU

tH

tSU

tH

VIH

VT

VIH

VT

VIH

VT

VIH

VT

LVC Link

LOW-HIGH-LOW

PULSE

HIGH-LOW-HIGH

PULSE

VT

tW

VT

LVC Link

CONTROL

INPUT

tPLZ

0V

OUTPUT

NORMALLY

LOW

tPZH

0V

SWITCH

CLOSED

OUTPUT

NORMALLY

HIGH

ENABLE

DISABLE

SWITCH

OPEN

tPHZ

0V

V

OL+VLZ

VOH

VT

VT

tPZL

VLOAD/2

VLOAD/2

VIH

VT

VOL

VOH-VHZ

LVC Link

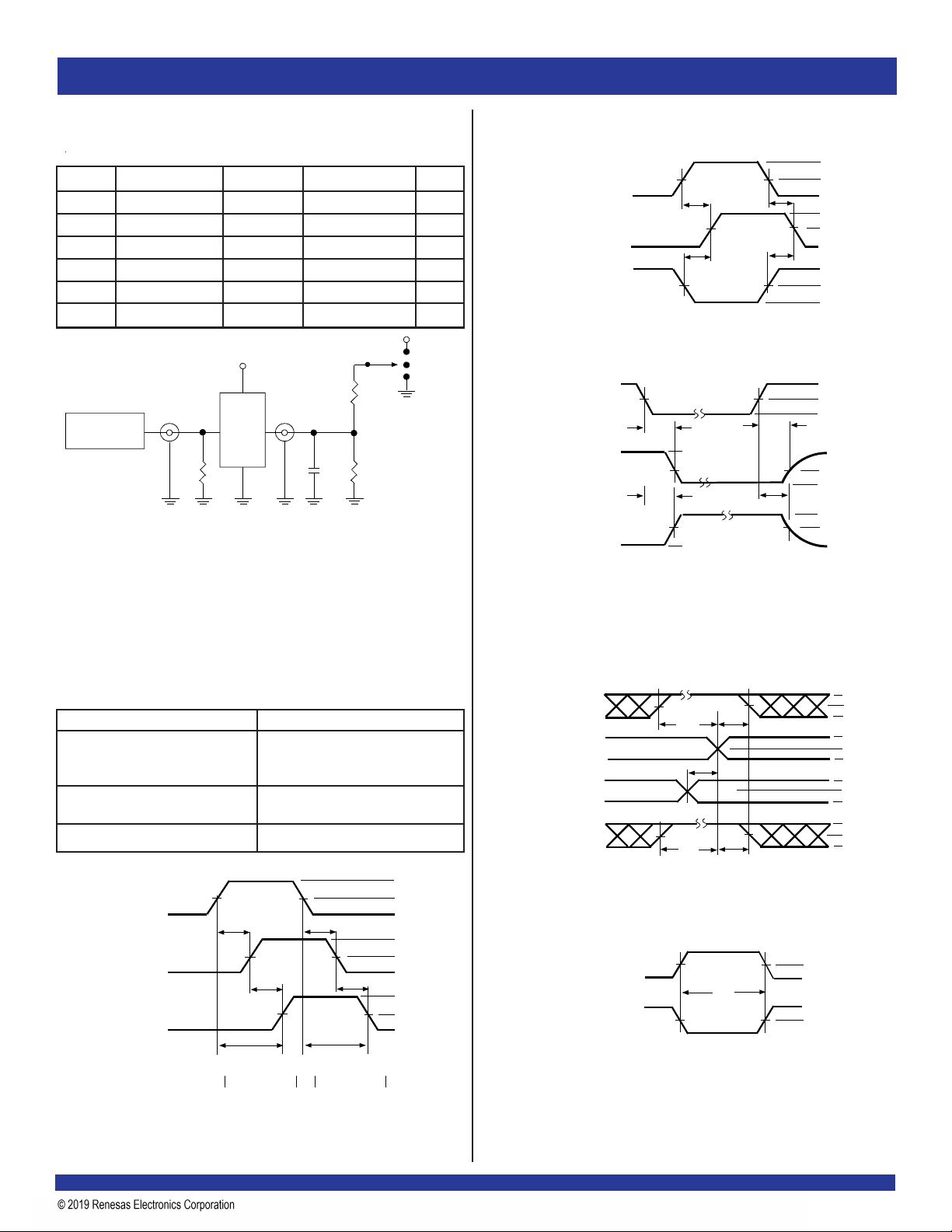

TEST CIRCUITS AND WAVEFORMS

Propagation Delay

Test Circuit for All Outputs

Enable and Disable Times

Set-up, Hold, and Release Times

NOTES:

1. For tSK(o) OUTPUT1 and OUTPUT2 are any two outputs.

2. For tSK(b) OUTPUT1 and OUTPUT2 are in the same bank.

DEFINITIONS:

CL = Load capacitance: includes jig and probe capacitance.

RT = Termination resistance: should be equal to ZOUT of the Pulse Generator.

NOTES:

1. Pulse Generator for All Pulses: Rate ≤ 10MHz; tF ≤ 2.5ns; tR ≤ 2.5ns.

2. Pulse Generator for All Pulses: Rate ≤ 10MHz; tF ≤ 2ns; tR ≤ 2ns.

Output Skew - tSK(X)

Pulse Width

NOTE:

1. Diagram shown for input Control Enable-LOW and input Control Disable-HIGH.

Symbol VCC

(1)

= 3.3V±0.3V VCC

(1)

= 2.7V VCC

(2)

= 2.5V±0.2V Unit

VLOAD 6 6 2 x Vcc V

VIH 2.7 2.7 Vcc V

VT 1.5 1.5 Vcc / 2 V

VLZ 300 300 150 mV

VHZ 300 300 150 mV

C

L 50 50 30 pF

TEST CONDITIONS

SWITCH POSITION

Test Switch

Open Drain

Disable Low V

LOAD

Enable Low

Disable High GND

Enable High

All Other Tests Open

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件