Datasheet 搜索 > 逻辑控制器 > Fairchild(飞兆/仙童) > 74LVT16245MEAX 数据手册 > 74LVT16245MEAX 数据手册 1/8 页

器件3D模型

器件3D模型¥ 7.264

74LVT16245MEAX 数据手册 - Fairchild(飞兆/仙童)

制造商:

Fairchild(飞兆/仙童)

分类:

逻辑控制器

封装:

SSOP-48

描述:

低电压16位收发器与3态输出 Low Voltage 16-Bit Transceiver with 3-STATE Outputs

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

74LVT16245MEAX数据手册

Page:

of 8 Go

若手册格式错乱,请下载阅览PDF原文件

© 2005 Fairchild Semiconductor Corporation DS500152 www.fairchildsemi.com

January 1999

Revised June 2005

74LVT16245 • 74LVTH16245 Low Voltage 16-Bit Transceiver with 3-STATE Outputs

74LVT16245 • 74LVTH16245

Low Voltage 16-Bit Transceiver with 3-STATE Outputs

General Description

The LVT16245 and LVTH16245 contain sixteen non-invert-

ing bidirectional buffers with 3-STATE outputs and is

intended for bus oriented applications. The device is byte

controlled. Each byte has separate control inputs which

can be shorted together for full 16-bit operation. The T/R

inputs determine the direction of data flow through the

device. The OE

inputs disable both the A and B ports by

placing them in a high impedance state.

The LVTH16245 data inputs include bushold, eliminating

the need for external pull-up resistors to hold unused

inputs.

These non-inverting transceivers are designed for low-volt-

age (3.3V) V

CC

applications, but with the capability to pro-

vide a TTL interface to a 5V environment. The LVT16245

and LVTH16245 are fabricated with an advanced BiCMOS

technology to achieve high speed operation similar to 5V

ABT while maintaining low power dissipation.

Features

■ Input and output interface capability to systems at

5V V

CC

■ Bushold data inputs eliminate the need for external

pull-up resistors to hold unused inputs (74LVTH16245),

also available without bushold feature (74LVT16245).

■ Live insertion/extraction permitted

■ Power Up/Down high impedance provides glitch-free

bus loading

■ Outputs source/sink

32 mA/

64 mA

■ Functionally compatible with the 74 series 16245

■ Latch-up performance exceeds 500 mA

■ ESD performance:

Human-body model

!

2000V

Machine model

!

200V

Charged-device

!

1000V

■ Also packaged in plastic Fine-Pitch Ball Grid Array

(FBGA) (Preliminary)

Ordering Code:

Note 1: BGA package available in Tape and Reel only.

Note 2: Devices also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.

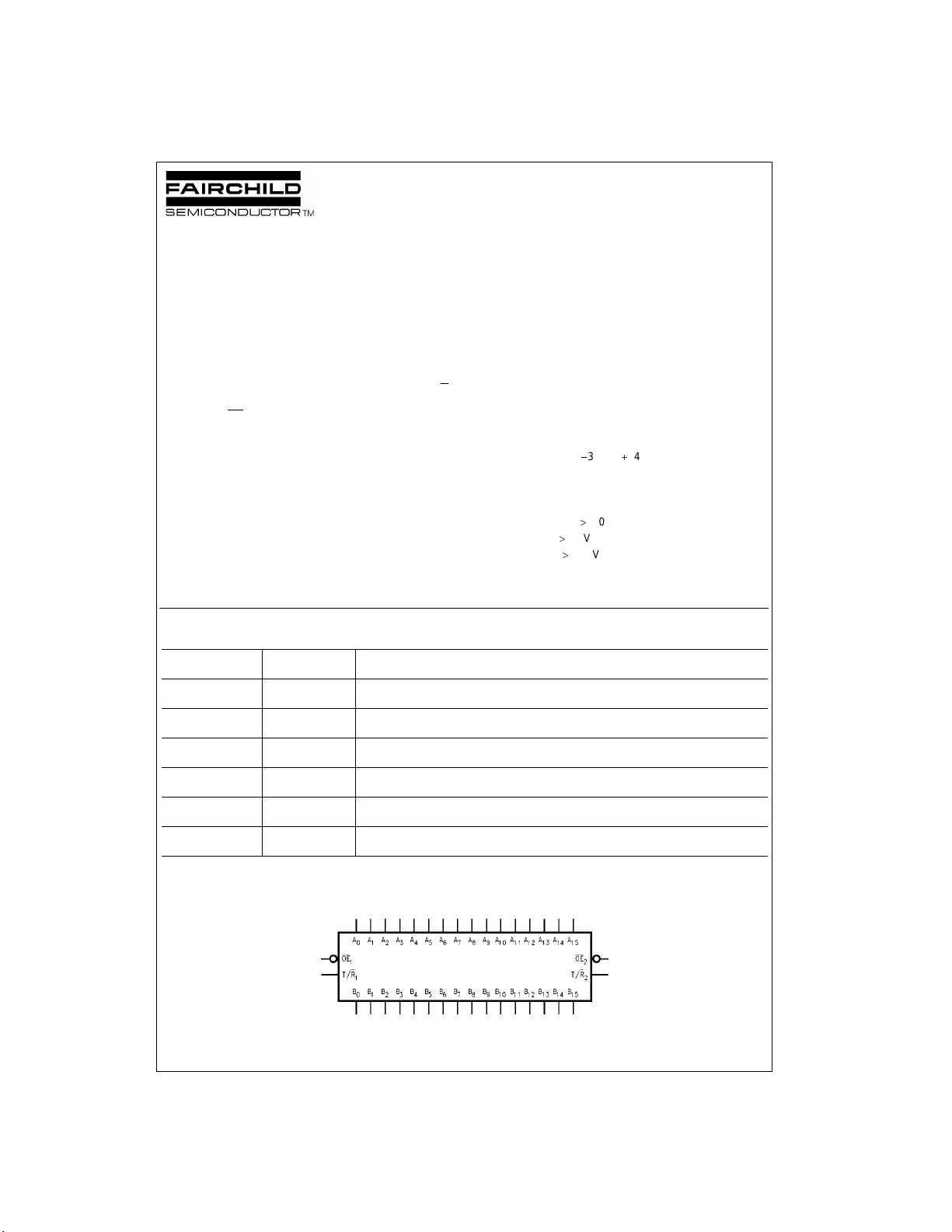

Logic Symbol

Order Number

Package

Number

Package Description

74LVT16245GX

(Note 1)

BGA54A

(Preliminary)

54-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide

[Tape and Reel]

74LVT16245MEA

(Note 2)

MS48A 48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" Wide

74LVT16245MTD

(Note 2)

MTD48 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

74LVTH16245GX

(Note 1)

BGA54A

(Preliminary)

54-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide

[Tape and Reel]

74LVTH16245MEA

(Note 2)

MS48A 48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" Wide

74LVTH16245MTD

(Note 2)

MTD48 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件