Datasheet 搜索 > AD转换器 > ADI(亚德诺) > AD7401YRWZ 数据手册 > AD7401YRWZ 数据手册 3/20 页

器件3D模型

器件3D模型¥ 1.3

AD7401YRWZ 数据手册 - ADI(亚德诺)

制造商:

ADI(亚德诺)

分类:

AD转换器

封装:

SOIC-16

描述:

ANALOG DEVICES AD7401YRWZ 模数转换器, 16 bit, 16 MSPS, 3 V, 5.25 V, SOIC

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

AD7401YRWZ数据手册

Page:

of 20 Go

若手册格式错乱,请下载阅览PDF原文件

Data Sheet AD7401

Rev. E | Page 3 of 20

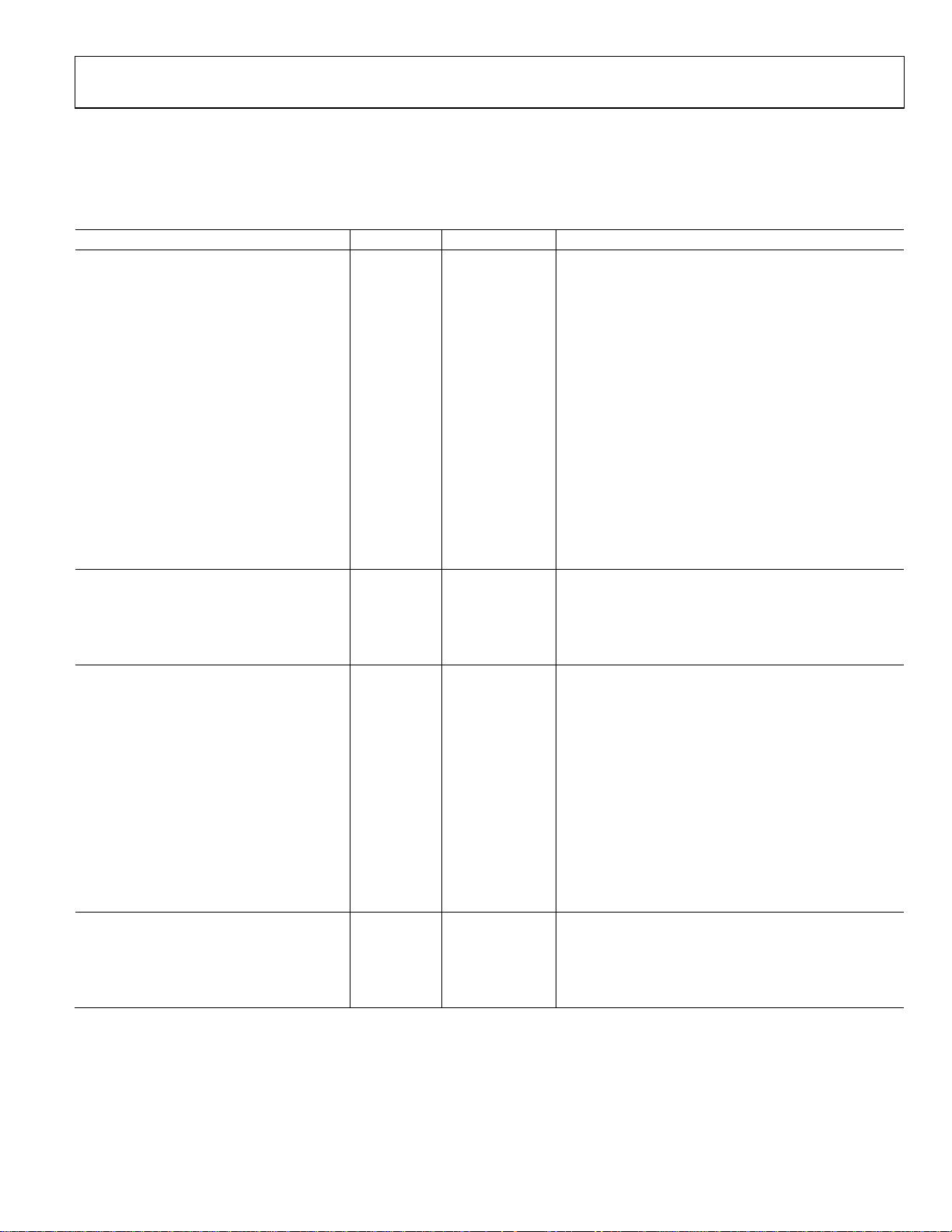

SPECIFICATIONS

V

DD1

= 4.5 V to 5.25 V, V

DD2

= 3 V to 5.5 V, V

IN

+ = −200 mV to +200 mV, and V

IN

− = 0 V (single-ended); T

A

= T

MIN

to T

MAX

,

f

MCLK

= 16 MHz maximum, tested with Sinc

3

filter, 256 decimation rate, as defined by Verilog code, unless otherwise noted.

Table 1.

Parameter Y Version

1, 2

Unit Test Conditions/Comments

STATIC PERFORMANCE

Resolution

16 Bits min Filter output truncated to 16 bits

Integral Nonlinearity

3

±15 LSB max −40°C to +85°C; ±2 LSB typical; f

MCLK

= 20 MHz maximum

4

±25 LSB max >85°C to 105°C

±55 LSB max f

MCLK

= 20 MHz maximum

4

; V

IN

+ = −250 mV to +250 mV

Differential Nonlinearity

3

±0.9

LSB max

Guaranteed no missed codes to 16 bits;

f

MCLK

= 20 MHz maximum

4

; V

IN

+ = −250 mV to +250 mV

Offset Error

3

±0.6 mV max f

MCLK

= 20 MHz maximum

4

; V

IN

+ = −250 mV to +250 mV

±50 µV typ T

A

= 25°C

Offset Drift vs. Temperature

3.5 µV/°C max −40°C to +105°C

1 µV/°C typ

Offset Drift vs. V

DD1

120

µV/V typ

Gain Error

3

±1.6 mV max −40°C to +85°C

±2 mV max >85°C to 105°C

±1 mV typ f

MCLK

= 20 MHz maximum

4

; V

IN

+ = −250 mV to +250 mV

Gain Error Drift vs. Temperature 23 µV/°C typ −40°C to +105°C

Gain Error Drift vs. V

DD1

110 µV/V typ

ANALOG INPUT

Input Voltage Range

±200 mV min/mV max For specified performance; full range ±320 mV

Dynamic Input Current ±9 µA max V

IN

+ = 400 mV, V

IN

− = 0 V

DC Leakage Current ±0.5 µA max

Input Capacitance 10 pF typ

DYNAMIC SPECIFICATIONS

V

IN

+ = 5 kHz, 400 mV p-p sine

Signal-to-(Noise + Distortion) Ratio (SINAD)

3

70 dB min −40°C to +85°C; f

MCLK

= 9 MHz to 20 MHz

4

68 dB min −40°C to +85°C; f

MCLK

= 5 MHz to <9 MHz

65 dB min >85°C to 105°C

65 dB min f

MCLK

= 20 MHz maximum

4

; V

IN

+ = −250 mV to +250 mV

81 dB typ

Signal-to-Noise Ratio (SNR) 80 dB min −40°C to +105°C; 82 dB typ

80 dB min f

MCLK

= 20 MHz maximum

4

; V

IN

+ = −250 mV to +250 mV

Total Harmonic Distortion (THD)

3

−92 dB typ f

MCLK

= 20 MHz maximum

4

; V

IN

+ = −250 mV to +250 mV

Peak Harmonic or Spurious Noise (SFDR)

3

−92 dB typ

Effective Number of Bits (ENOB)

3

11.5 Bits

Isolation Transient Immunity

3

25 kV/µs min

30 kV/µs typ

LOGIC INPUTS

Input High Voltage, V

IH

0.8 × V

DD2

V min

Input Low Voltage, V

IL

0.2 × V

DD2

V max

Input Current, I

IN

±0.5 µA max

Input Capacitance, C

IN

5

10 pF max

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件