Datasheet 搜索 > 存储芯片 > ATMEL(爱特美尔) > AT45DB041B-TC 数据手册 > AT45DB041B-TC 数据手册 5/35 页

器件3D模型

器件3D模型¥ 8.063

AT45DB041B-TC 数据手册 - ATMEL(爱特美尔)

制造商:

ATMEL(爱特美尔)

分类:

存储芯片

封装:

TSOP-28

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

AT45DB041B-TC数据手册

Page:

of 35 Go

若手册格式错乱,请下载阅览PDF原文件

5

3443C–DFLSH–5/05

AT45DB041B

A low-to-high transition on the CS pin will terminate the read operation and tri-state the SO pin.

The maximum SCK frequency allowable for the Continuous Array Read is defined by the f

CAR

specification. The Continuous Array Read bypasses both data buffers and leaves the contents

of the buffers unchanged.

5.1.2 Main Memory Page Read

A Main Memory Page Read allows the user to read data directly from any one of the 2048 pages

in the main memory, bypassing both of the data buffers and leaving the contents of the buffers

unchanged. To start a page read, an opcode of 52H or D2H must be clocked into the device fol-

lowed by 24 address bits and 32 don’t care bits. The first four bits of the 24-bit address

sequence are reserved bits, the next 11 address bits (PA10 - PA0) specify the page address,

and the next nine address bits (BA8 - BA0) specify the starting byte address within the page.

The 32 don’t care bits which follow the 24 address bits are sent to initialize the read operation.

Following the 32 don’t care bits, additional pulses on SCK result in serial data being output on

the SO (serial output) pin. The CS

pin must remain low during the loading of the opcode, the

address bits, the don’t care bits, and the reading of data. When the end of a page in main mem-

ory is reached during a Main Memory Page Read, the device will continue reading at the

beginning of the same page. A low-to-high transition on the CS

pin will terminate the read oper-

ation and tri-state the SO pin.

5.1.3 Buffer Read

Data can be read from either one of the two buffers, using different opcodes to specify which

buffer to read from. An opcode of 54H or D4H is used to read data from buffer 1, and an opcode

of 56H or D6H is used to read data from buffer 2. To perform a Buffer Read, the eight bits of the

opcode must be followed by 15 don’t care bits, nine address bits, and eight don’t care bits. Since

the buffer size is 264 bytes, nine address bits (BFA8 - BFA0) are required to specify the first byte

of data to be read from the buffer. The CS

pin must remain low during the loading of the opcode,

the address bits, the don’t care bits, and the reading of data. When the end of a buffer is

reached, the device will continue reading back at the beginning of the buffer. A low-to-high tran-

sition on the CS

pin will terminate the read operation and tri-state the SO pin.

5.1.4 Status Register Read

The status register can be used to determine the device’s Ready/Busy status, the result of a

Main Memory Page to Buffer Compare operation, or the device density. To read the status reg-

ister, an opcode of 57H or D7H must be loaded into the device. After the last bit of the opcode is

shifted in, the eight bits of the status register, starting with the MSB (bit 7), will be shifted out on

the SO pin during the next eight clock cycles. The five most significant bits of the status register

will contain device information, while the remaining three least-significant bits are reserved for

future use and will have undefined values. After bit 0 of the status register has been shifted out,

the sequence will repeat itself (as long as CS

remains low and SCK is being toggled) starting

again with bit 7. The data in the status register is constantly updated, so each repeating

sequence will output new data.

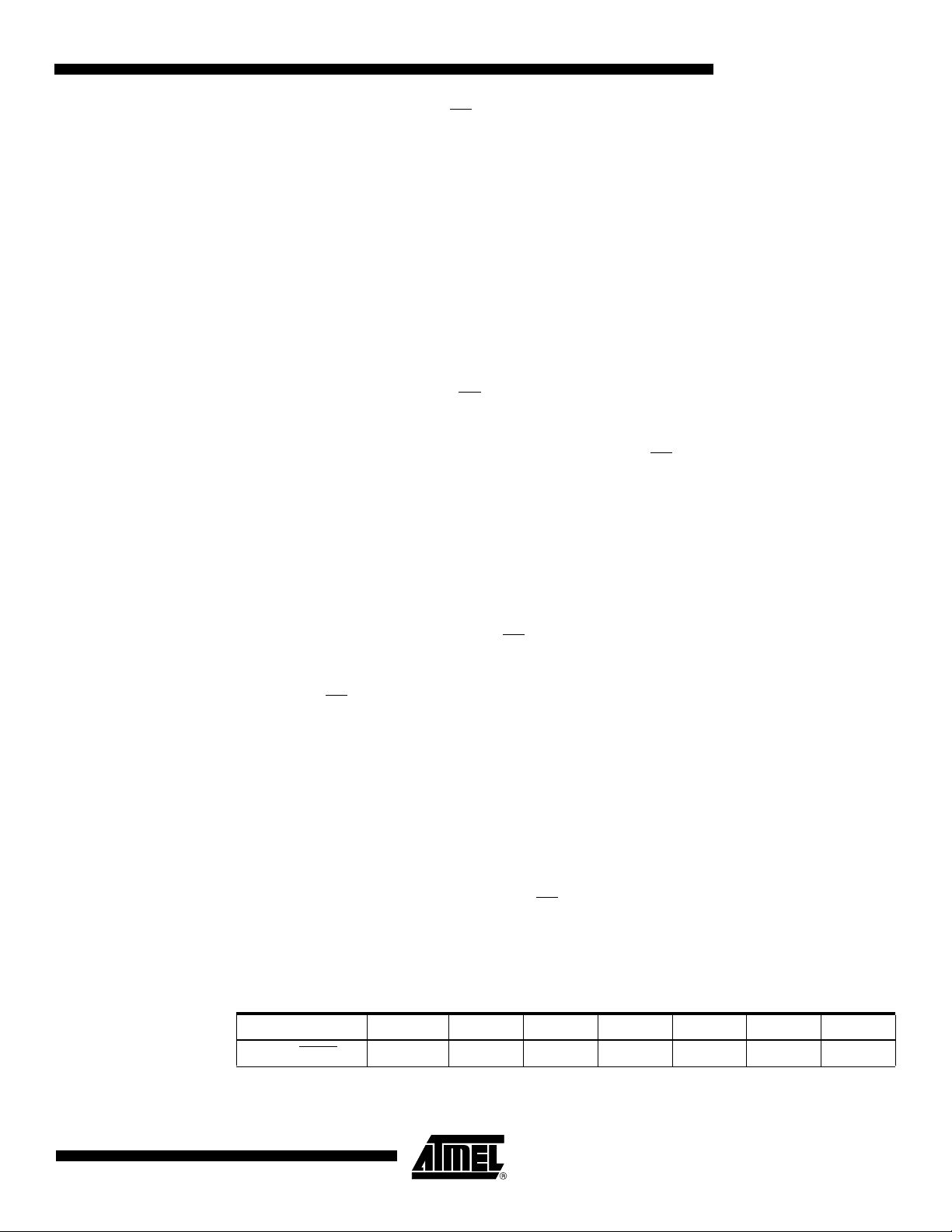

Table 5-1. Status Register Format

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

RDY/BUSY

COMP0111XX

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件