Datasheet 搜索 > 微控制器 > ATMEL(爱特美尔) > AT89LP52-20JU 数据手册 > AT89LP52-20JU 数据手册 12/118 页

器件3D模型

器件3D模型¥ 10.565

AT89LP52-20JU 数据手册 - ATMEL(爱特美尔)

制造商:

ATMEL(爱特美尔)

分类:

微控制器

封装:

PLCC-44

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

AT89LP52-20JU数据手册

Page:

of 118 Go

若手册格式错乱,请下载阅览PDF原文件

12

3709D–MICRO–12/11

AT89LP51/52

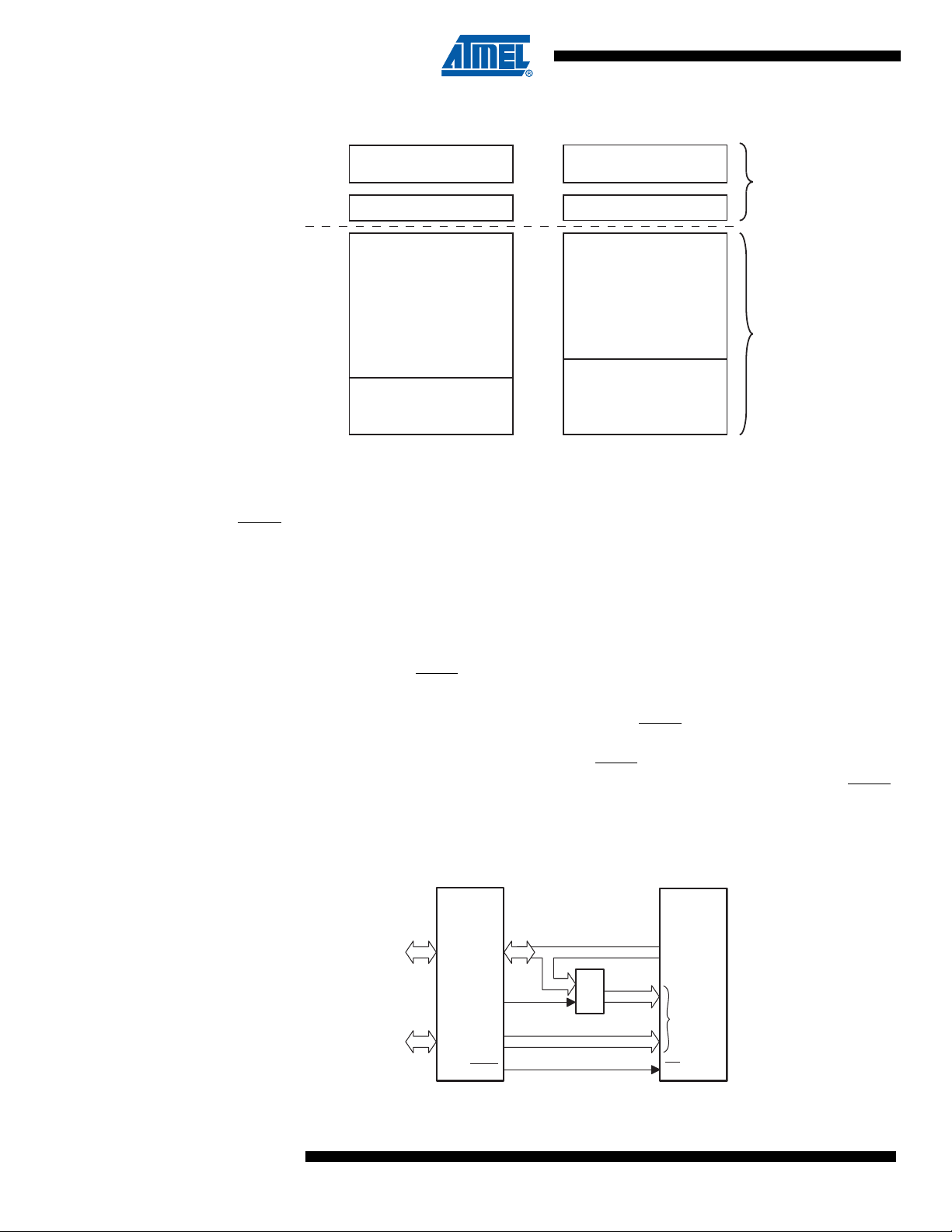

Figure 3-1. Program Memory Map

3.1.1 External Program Memory Interface

The AT89LP51/52 uses the standard 8051 external program memory interface with the upper

address on Port 2, the lower address and data in/out multiplexed on Port 0, and the ALE and

PSEN

strobes. Program memory addresses are always 16-bits wide, even though the actual

amount of program memory used may be less than 64K byes. External program execution sacri-

fices two full 8-bit ports, P0 and P2, to the function of addressing the program memory.

Figure 3-2 shows a hardware configuration for a

ccessing up to 64K bytes of external ROM using

a 16-bit linear address. Port 0 serves as a multiplexed address/data bus to the ROM. The

Address Latch Enable strobe (ALE) is used to latch the lower address byte into an external reg-

ister so that Port 0 can b e freed for data inpu t/output. Port 2 provides the upper address byte

throughou t the operation. PSEN strobes the external memory.

Figure 3-3 shows the timing of the external program memory interface. ALE is emitted at a con-

stant rate of 1/3 of the system clock with a 1/3 duty cycle. PSEN

is emitted at a similar rate, but

with 50% duty cycle. The new address changes in the middle of the ALE pulse for latching on

the falling edge and is tristated at the falling edge of PSEN

. The instruction data is sampled from

P0 and latched internally during the high phase of the clock prior to the rising edge of PSEN

.

This timing applies to both Compatibility a nd Fast modes. In Compatibility mode there is no dif-

ference in instruction timing between internal and external execution.

Figure 3-2. Executing from External Program Memory

0000

FFFF

0000

007F

User Signature Array

0100

01FF

Atmel Signature Array

SIGEN=0

SIGEN=1

AT89LP52

2000

1FFF

External Program

Memory

(XCODE: 56KB)

Internal Program

Memory

(CODE: 8KB)

0000

FFFF

0000

007F

User Signature Array

0100

01FF

Atmel Signature Array

AT89LP51

1000

0FFF

External Program

Memory

(XCODE: 60KB)

Internal Program

Memory

(CODE: 4KB)

AT89LP EXTERNAL

PROGRAM

MEMORY

INSTR.

ADDR

OEPSEN

P3

P2

ALE

P0P1

LATCH

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件