Datasheet 搜索 > 逻辑控制器 > TI(德州仪器) > CD74HCT4520MT 数据手册 > CD74HCT4520MT 数据手册 6/17 页

器件3D模型

器件3D模型¥ 2.615

CD74HCT4520MT 数据手册 - TI(德州仪器)

制造商:

TI(德州仪器)

分类:

逻辑控制器

封装:

SOIC-16

描述:

高速CMOS逻辑双路同步计数器 High-Speed CMOS Logic Dual Synchronous Counters

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

CD74HCT4520MT数据手册

Page:

of 17 Go

若手册格式错乱,请下载阅览PDF原文件

6

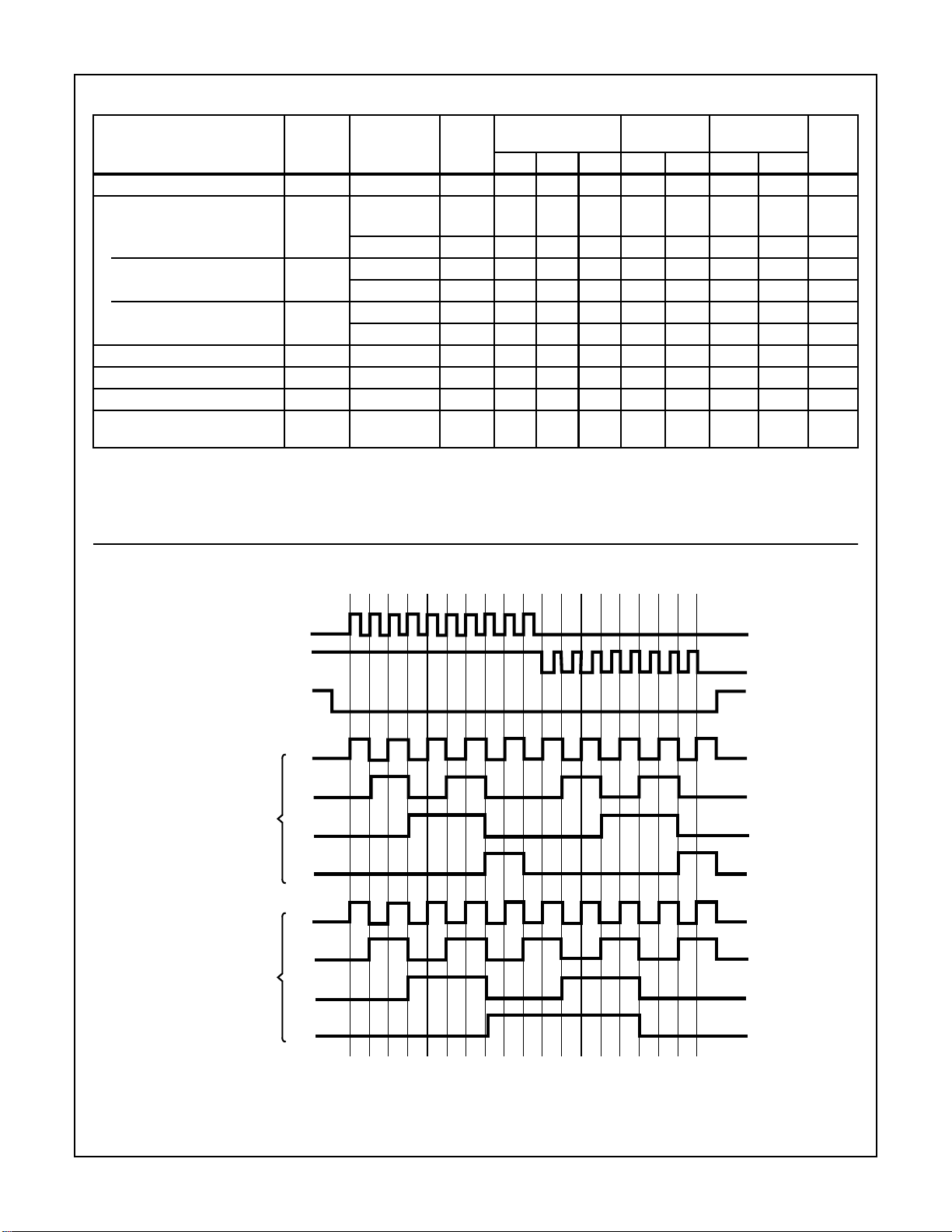

HCT TYPES

Propagation Delay

CP to Q

n

t

PLH,

t

PHL

C

L

= 50pF 4.5 - - 53 - 66 - 80 ns

C

L

= 15pF 5 - 22 - - - - - ns

Enable to Q

n

t

PLH,

t

PHL

C

L

= 50pF 4.5 - - 55 - 69 - 83 ns

C

L

= 15pF 5 - 23 - - - - - ns

MR to Q

n

t

PLH,

t

PHL

C

L

= 50pF 4.5 - - 35 - 44 - 53 ns

C

L

= 15pF 5 - 14 - - - - - ns

Output Transition Time t

THL

,t

TLH

C

L

= 50pF 4.5 - - 15 - 19 - 22 ns

Input Capacitance C

IN

C

L

= 50pF - - - 10 - 10 - 10 pF

Maximum Clock Frequency f

MAX

CL = 15pF 5 - 50 - - - - - MHz

Power Dissipation Capacitance

(Note 3,4)

C

PD

-5-33-----pF

NOTES:

3. C

PD

is used to determine the dynamic power consumption, per counter.

4. P

D

= V

CC

2

f

i

(C

PD

+ C

L

) where f

i

= Input Frequency, C

L

= Output Load Capacitance, V

CC

= Supply Voltage.

Switching Specifications Input t

r

, t

f

= 6ns (Continued)

PARAMETER SYMBOL

TEST

CONDITIONS V

CC

(V)

25

o

C

-40

o

C TO

85

o

C -55

o

C TO 125

o

C

UNITSMIN TYP MAX MIN MAX MIN MAX

Timing Diagram

FIGURE 1.

CLOCK

ENABLE

MASTER RESET

HC4518

’HC/HCT4520

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18

Q

1

Q

2

Q

3

Q

4

Q

1

Q

2

Q

3

Q

4

12345678901234567890

12345678910111213141501234

CD74HC4518, CD54HC4520, CD74HC4520, CD74HCT4520

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件