Datasheet 搜索 > 微控制器 > Microchip(微芯) > DSPIC30F2010-20E/SOG 数据手册 > DSPIC30F2010-20E/SOG 数据手册 92/202 页

器件3D模型

器件3D模型¥ 34.963

DSPIC30F2010-20E/SOG 数据手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

SOIC

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P5P95P192Hot

原理图在P8P15P53P58P62P63P67P71P75P82P92P96

标记信息在P185

封装信息在P148P185P190P192P201

功能描述在P91P95

技术参数、封装参数在P117P149P153P154P156P158P180P181P192

电气规格在P57P61P113P117P155P192

导航目录

DSPIC30F2010-20E/SOG数据手册

Page:

of 202 Go

若手册格式错乱,请下载阅览PDF原文件

dsPIC30F2010

DS70118J-page 92 © 2011 Microchip Technology Inc.

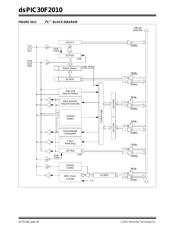

15.2 Framed SPI Support

The module supports a basic framed SPI protocol in

Master or Slave mode. The control bit FRMEN enables

framed SPI support and causes the SSx

pin to perform

the frame synchronization pulse (FSYNC) function.

The control bit SPIFSD determines whether the SSx

pin is an input or an output (i.e., whether the module

receives or generates the frame synchronization

pulse). The frame pulse is an active-high pulse for a

single SPI clock cycle. When frame synchronization is

enabled, the data transmission starts only on the

subsequent transmit edge of the SPI clock.

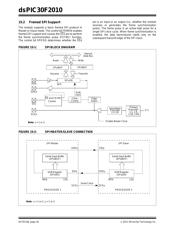

FIGURE 15-1: SPI BLOCK DIAGRAM

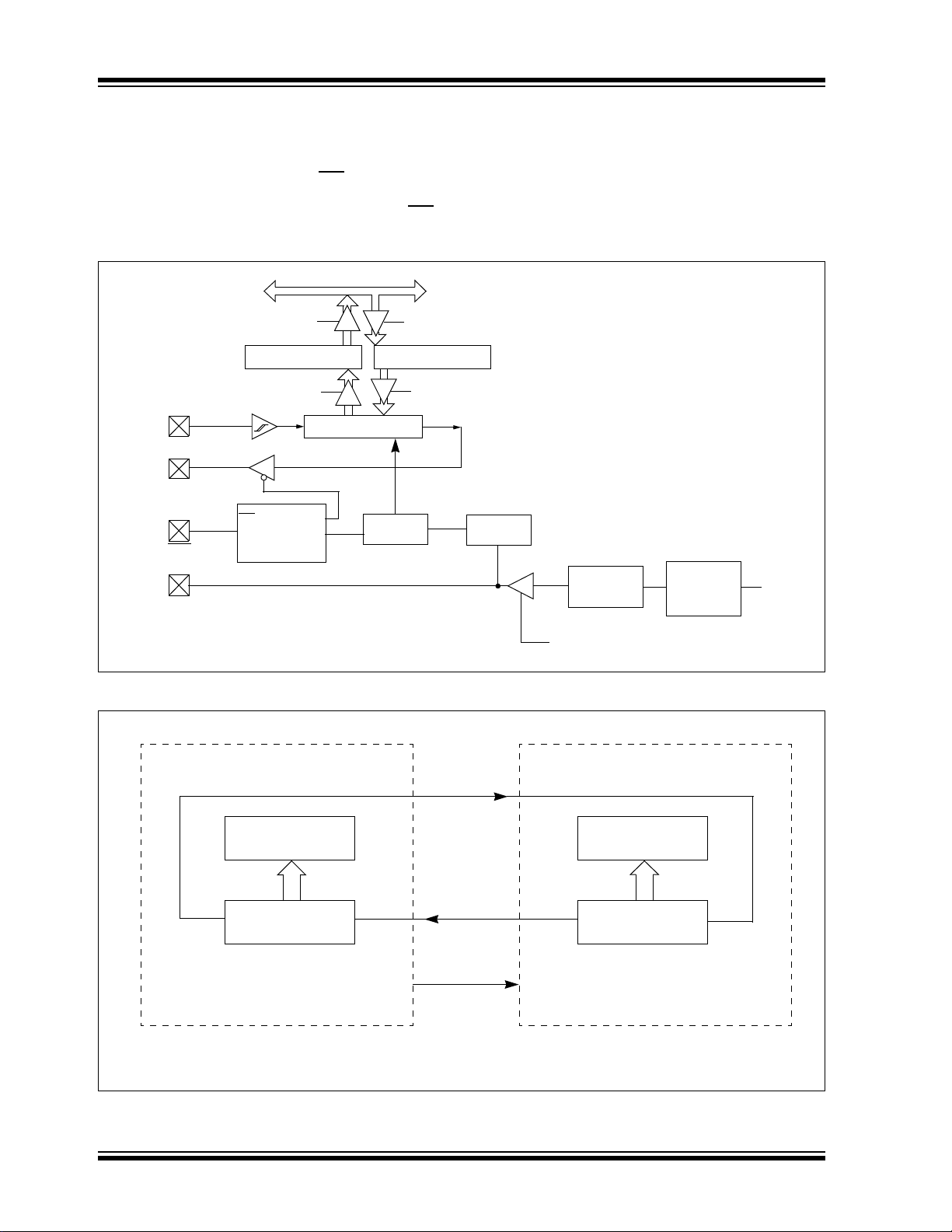

FIGURE 15-2: SPI MASTER/SLAVE CONNECTION

Note: x = 1 or 2.

Read Write

Internal

Data Bus

SDIx

SDOx

SSx

SCKx

SPIxSR

SPIxBUF

bit 0

Shift

clock

Edge

Select

F

CY

Primary

1:1, 1:4,

Enable Master Clock

Prescaler

Secondary

Prescaler

1:1-1:8

SS and FSYNC

Control

Clock

Control

Transmit

SPIxBUF

Receive

1:16, 1:64

Serial Input Buffer

(SPIxBUF)

Shift Register

(SPIxSR)

MSb

LSb

SDOx

SDIx

PROCESSOR 1

SCKx

SPI Master

Serial Input Buffer

(SPIyBUF)

Shift Register

(SPIySR)

LSb

MSb

SDIy

SDOy

PROCESSOR 2

SCKy

SPI Slave

Serial Clock

Note: x = 1 or 2, y = 1 or 2.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件