Datasheet 搜索 > FPGA芯片 > Altera(阿尔特拉) > EP2S15F484C3 数据手册 > EP2S15F484C3 数据手册 5/248 页

器件3D模型

器件3D模型¥ 2644.089

EP2S15F484C3 数据手册 - Altera(阿尔特拉)

制造商:

Altera(阿尔特拉)

分类:

FPGA芯片

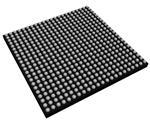

封装:

FBGA-484

描述:

FPGA - 现场可编程门阵列 FPGA - Stratix II 780 LABs 342 IOs

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

原理图在P20P25P61P144

封装尺寸在P247

型号编码规则在P7P247

功能描述在P19P20

技术参数、封装参数在P141P142P147P150P151P152P154P155P156P157P158P159

应用领域在P174P175P176P177P178P179

电气规格在P136P149

型号编号列表在P147

导航目录

EP2S15F484C3数据手册

Page:

of 248 Go

若手册格式错乱,请下载阅览PDF原文件

Altera Corporation v

Contents Contents

Timing Model ....................................................................................................................................... 5–20

Preliminary & Final Timing .......................................................................................................... 5–20

I/O Timing Measurement Methodology .................................................................................... 5–21

Performance .................................................................................................................................... 5–27

Internal Timing Parameters .......................................................................................................... 5–34

Stratix II Clock Timing Parameters .............................................................................................. 5–41

Clock Network Skew Adders .......................................................................................................5–50

IOE Programmable Delay ............................................................................................................. 5–51

Default Capacitive Loading of Different I/O Standards .......................................................... 5–52

I/O Delays ....................................................................................................................................... 5–54

Maximum Input & Output Clock Toggle Rate .......................................................................... 5–66

Duty Cycle Distortion ......................................................................................................................... 5–77

DCD Measurement Techniques ................................................................................................... 5–78

High-Speed I/O Specifications .......................................................................................................... 5–87

PLL Timing Specifications .................................................................................................................. 5–91

External Memory Interface Specifications ....................................................................................... 5–94

JTAG Timing Specifications ............................................................................................................... 5–96

Document Revision History ............................................................................................................... 5–97

Chapter 6. Reference & Ordering Information

Software .................................................................................................................................................. 6–1

Device Pin-Outs ..................................................................................................................................... 6–1

Ordering Information ........................................................................................................................... 6–1

Document Revision History ................................................................................................................. 6–2

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件