Datasheet 搜索 > FPGA芯片 > Altera(阿尔特拉) > EP3C5F256I7N 数据手册 > EP3C5F256I7N 数据手册 6/8 页

器件3D模型

器件3D模型¥ 301.059

EP3C5F256I7N 数据手册 - Altera(阿尔特拉)

制造商:

Altera(阿尔特拉)

分类:

FPGA芯片

封装:

FBGA-256

描述:

可编程逻辑器件(CPLD/FPGA) EP3C5F256I7N BGA-256

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

功能描述在P4

导航目录

EP3C5F256I7N数据手册

Page:

of 8 Go

若手册格式错乱,请下载阅览PDF原文件

Cyclone III FPGAs • March 2007 • www.altera.com6

Nios II embedded processor

Get the performance you need with the right feature set and keep costs down.

With the versatility of our Nios® II soft-core embedded processor, you can build

an exact-fit processor, customized for your application in minutes. A Nios II

processor implemented in a Cyclone III FPGA allows you to choose the exact set

of CPUs, peripherals, and interfaces that you need ,and to remotely upgrade in the

field. You can address changing requirements to stay competitive. You can also

increase performance without changing your board design—accelerating only

functions that need it and combining many functions onto one chip. With the

Nios II embedded processor, you’ll lower overall cost, design complexity, and

power consumption. Assemble an exact-fit processor system every time with the

world’s most versatile processor.

Low-cost development kits and free reference designs

The Cyclone III FPGA Starter Kit is available today to get your next design up

and running in hardware as quickly as possible. Whether your’re designing for

communications, embedded systems hardware or software, or vertical market areas

such as video and image processing, display, wireless, or another high-volume, cost-

sensitive application, Altera and partner development kits give you everything you

need to create and implement your design right out of the box.

Intellectual property

Altera and its partners provide

off-the-shelf intellectual

property (IP) cores. You can

use these pre-optimized cores

easily, reducing design and

test time.

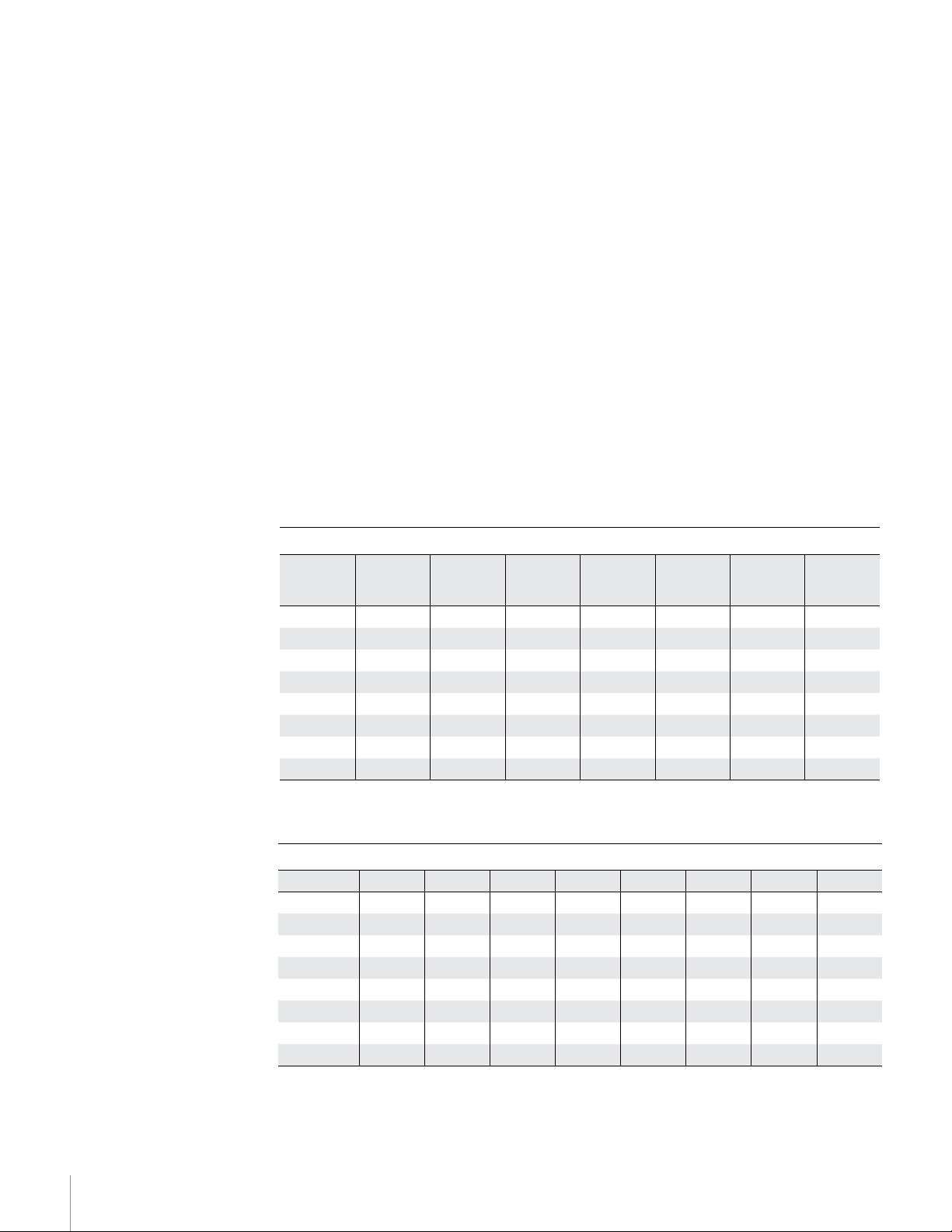

Cyclone III package overview

1

Device E144 Q240 F256 F324 F484 F780 U256 U484

EP3C5 94 182 182

EP3C10 94 182 182

EP3C16 84 160 168 346 168 346

EP3C25 82 148 156 215 156

EP3C40 128 195 331 535 331

EP3C55 327 377 217

EP3C80 295 429 295

EP3C120 283 531

Cyclone III device overview

Device LEs M9K

Memory

Blocks

Total

Memory

(Mbits)

Multipliers PLLs Total Global

Clocks

Maximum

User I/O

Pins

EP3C5 5,136 46 0.4 23 2 10 182

EP3C10 10,320 46 0.4 23 2 10 182

EP3C16 15,408 56 0.5 56 4 20 346

EP3C25 24,624 66 0.6 66 4 20 215

EP3C40 39,600 126 1.1 126 4 20 535

EP3C55 55,856 260 2.3 156 4 20 377

EP3C80 81,264 305 2.7 244 4 20 428

EP3C120 119,088 432 3.9 288 4 20 531

Device features

that deliver functionality.

A selection of low-cost packages

and user I/O pin counts.

1

For more information on packages, see Cyclone FPGA Series Package and I/O Matrix at www.altera.com/selectorguides.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件