Datasheet 搜索 > FPGA芯片 > Altera(阿尔特拉) > EP3SE110F1152I4N 数据手册 > EP3SE110F1152I4N 数据手册 6/332 页

器件3D模型

器件3D模型¥ 21.785

EP3SE110F1152I4N 数据手册 - Altera(阿尔特拉)

制造商:

Altera(阿尔特拉)

分类:

FPGA芯片

封装:

BBGA-1152

描述:

FPGA - 现场可编程门阵列 FPGA - Stratix III 4300 LABs 744 IOs

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

技术参数、封装参数在P1P2P5P6P8P9P10P11P12P13P14P15

电气规格在P1P2P3P4P5P6P7P8P9P10P11P12

导航目录

EP3SE110F1152I4N数据手册

Page:

of 332 Go

若手册格式错乱,请下载阅览PDF原文件

1–6 Chapter 1: Stratix III Device Datasheet: DC and Switching Characteristics

Electrical Characteristics

Stratix III Device Handbook, Volume 2 © July 2010 Altera Corporation

On-Chip Termination (OCT) Specifications

If you enable OCT calibration, calibration is automatically performed at power-up for

the I/Os connected to the calibration block. Ta ble 1–7 lists the Stratix III OCT

calibration block accuracy specifications.

High overdrive

current

I

ODH

0V <V

IN

<V

CCIO

— -120 — -160 — -200 — -300 — -500 µA

Bus-hold trip

point

V

TRIP

— 0.45 0.95 0.50 1.00 0.68 1.07 0.70 1.70 0.80 2.00 V

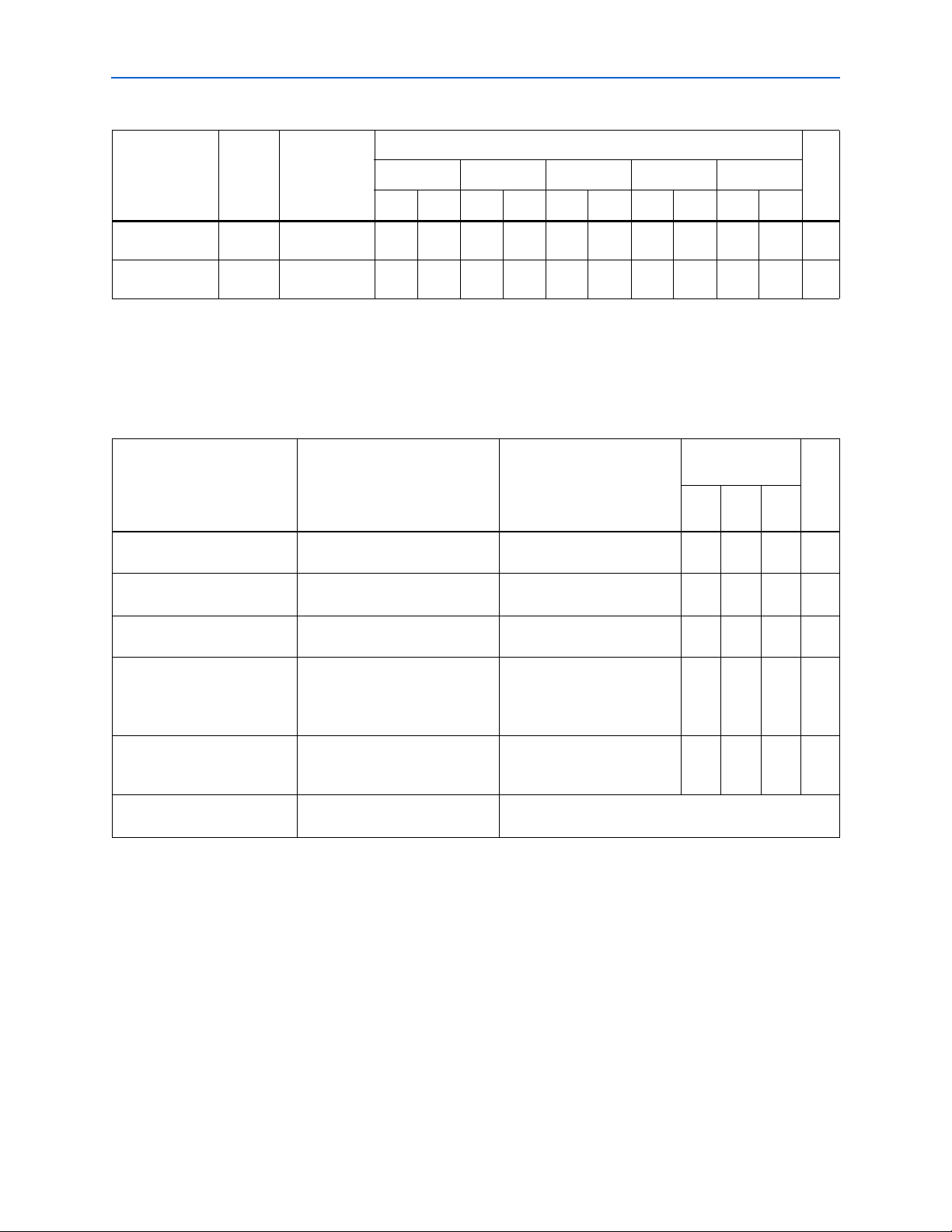

Table 1–6. Bus Hold Parameters for Stratix III Devices (Part 2 of 2)

Parameter Symbol Conditions

V

CCIO

Unit1.2 V 1.5 V 1.8 V 2.5 V 3.0 V/3.3 V

Min Max Min Max Min Max Min Max Min Max

Table 1–7. On-Chip Termination Calibration Accuracy Specifications for Stratix III Devices (Note 1)

Symbol Description Conditions

Calibration

Accuracy

Unit

C2

C3,

I3

C4,

I4

25- R

S

(2)

3.3, 3.0, 2.5, 1.8, 1.5, 1.2

Internal series termination with

calibration (25- setting)

V

CCIO

=

3.3, 3.0, 2.5, 1.8, 1.5, 1.2 V

±8 ±8 ±8 %

50- R

S

3.3, 3.0, 2.5, 1.8, 1.5, 1.2

Internal series termination with

calibration (50- setting)

V

CCIO

=

3.3, 3.0, 2.5, 1.8, 1.5, 1.2 V

±8 ±8 ±8 %

50- R

T

2.5, 1.8, 1.5, 1.2

Internal parallel termination with

calibration (50- setting)

V

CCIO

= 2.5, 1.8, 1.5, 1.2 V ±10 ±10 ±10 %

20-R

S

to 60-R

S

3.3, 3.0, 2.5, 1.8, 1.5, 1.2

Expanded range for internal

series termination with

calibration

(Between 20- to 60-setting)

V

CCIO

=

3.3, 3.0, 2.5, 1.8, 1.5, 1.2 V

(3)

±10 ±10 ±10 %

25- R

S _left_shift

Internal left shift series

termination with calibration

(25- R

S _left_shift

setting)

V

CCIO

=

3.3, 3.0, 2.5, 1.8, 1.5, 1.2 V

±10 ±10 ±10 %

R

OCT_CAL

Internal series termination with

calibration

(4)

Notes to Table 1–7:

(1) OCT calibration accuracy is valid at the time of calibration only.

(2) 25-

R

S

not supported for 1.5 V and 1.2 V in Row I/O.

(3) 1.5 V and 1.2 V only supports 40-

to 60- expanded range.

(4) For resistance tolerance after power-up calibration, refer to Equation 1–1 and Table 1–9 on page 1–8.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件