Datasheet 搜索 > Intel(英特尔) > EP4CE6E22I8LN 数据手册 > EP4CE6E22I8LN 数据手册 32/490 页

器件3D模型

器件3D模型¥ 130.242

EP4CE6E22I8LN 数据手册 - Intel(英特尔)

制造商:

Intel(英特尔)

封装:

LQFP-144

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P72P149P213P249P265P281Hot

典型应用电路图在P9P17P18P22P29P30P31P32P33P34P233

原理图在P41P82P83P234P250P254P285P286P290P293P295P297

型号编码规则在P26

封装信息在P26P153

功能描述在P233

技术参数、封装参数在P63P103P153P265P266P448P454P457P458P459P460P461

应用领域在P93P249

电气规格在P447

导航目录

EP4CE6E22I8LN数据手册

Page:

of 490 Go

若手册格式错乱,请下载阅览PDF原文件

2–4 Chapter 2: Logic Elements and Logic Array Blocks in Cyclone IV Devices

LE Operating Modes

Cyclone IV Device Handbook, November 2009 Altera Corporation

Volume 1

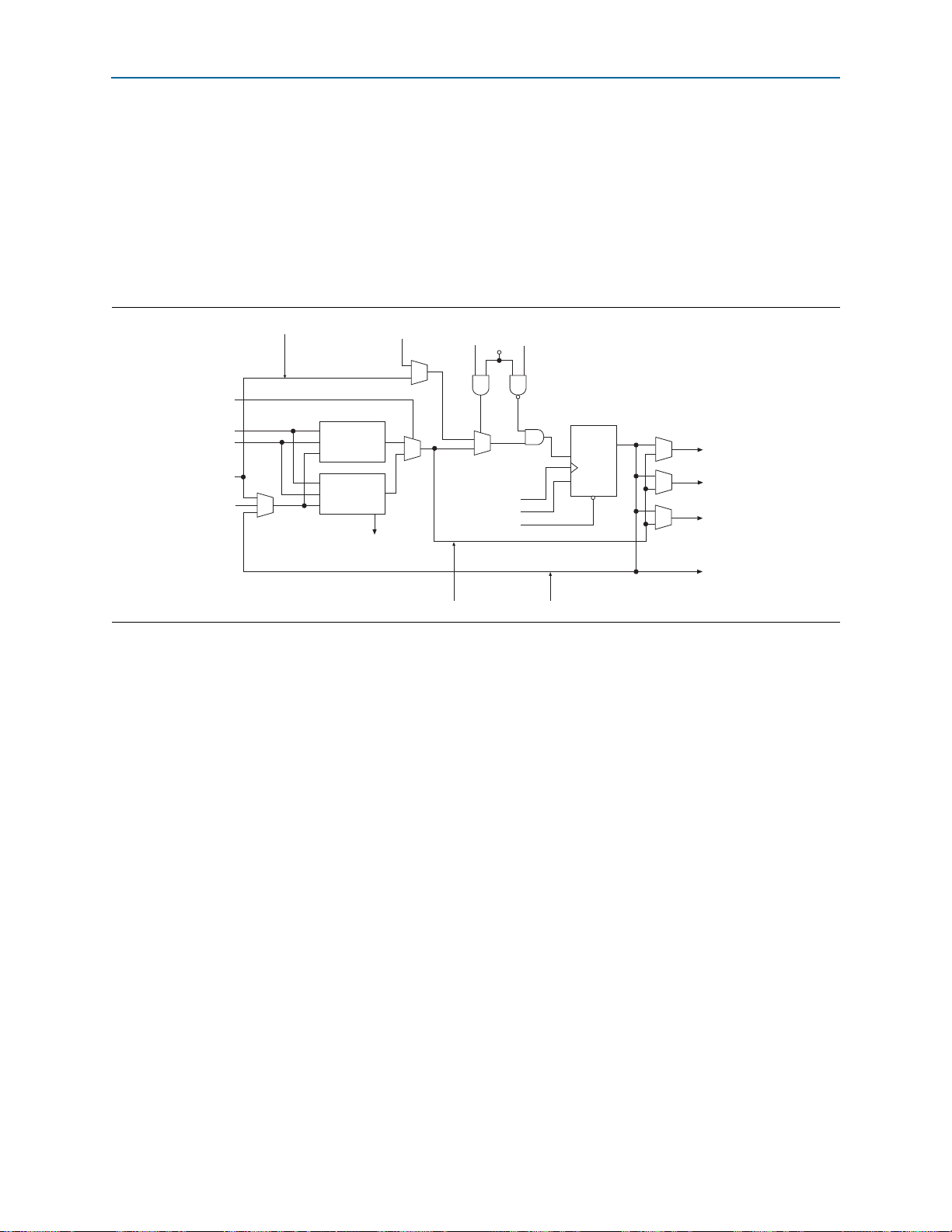

Arithmetic Mode

Arithmetic mode is ideal for implementing adders, counters, accumulators, and

comparators. An LE in arithmetic mode implements a 2-bit full adder and basic carry

chain (Figure 2–3). LEs in arithmetic mode can drive out registered and unregistered

versions of the LUT output. Register feedback and register packing are supported

when LEs are used in arithmetic mode.

Figure 2–3 shows LEs in arithmetic mode.

The Quartus II Compiler automatically creates carry chain logic during design

processing. You can also manually create the carry chain logic during design entry.

Parameterized functions, such as LPM functions, automatically take advantage of

carry chains for the appropriate functions.

The Quartus II Compiler creates carry chains longer than 16 LEs by automatically

linking LABs in the same column. For enhanced fitting, a long carry chain runs

vertically, which allows fast horizontal connections to M9K memory blocks or

embedded multipliers through direct link interconnects. For example, if a design has a

long carry chain in an LAB column next to a column of M9K memory blocks, any LE

output can feed an adjacent M9K memory block through the direct link interconnect.

If the carry chains run horizontally, any LAB which is not next to the column of M9K

memory blocks uses other row or column interconnects to drive a M9K memory

block. A carry chain continues as far as a full column.

Figure 2–3. Cyclone IV Device LEs in Arithmetic Mode

clock (LAB Wide)

ena (LAB Wide)

aclr (LAB Wide)

CLRN

D

Q

ENA

sclear

(LAB Wide)

sload

(LAB Wide)

Register

Chain Output

Row, Column, and

Direct link routing

Row, Column, and

Direct link routing

Local Routing

Register Feedback

Three-Input

LUT

Three-Input

LUT

cin (from cout

of previous LE)

data2

data1

cout

Register Bypass

data4

data3

Register Chain

Connection

Packed Register Input

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件