Datasheet 搜索 > Lattice Semiconductor(莱迪思) > GAL22V10C-10LJI 数据手册 > GAL22V10C-10LJI 数据手册 3/29 页

¥ 37.146

GAL22V10C-10LJI 数据手册 - Lattice Semiconductor(莱迪思)

制造商:

Lattice Semiconductor(莱迪思)

封装:

QCCJ

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

GAL22V10C-10LJI数据手册

Page:

of 29 Go

若手册格式错乱,请下载阅览PDF原文件

Specifications GAL22V10

3

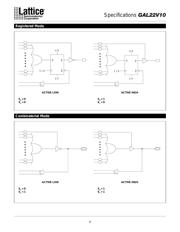

GAL22V10 OUTPUT LOGIC MACROCELL (OLMC)

Each of the Macrocells of the GAL22V10 has two primary functional

modes: registered, and combinatorial I/O. The modes and the

output polarity are set by two bits (SO and S1), which are normally

controlled by the logic compiler. Each of these two primary modes,

and the bit settings required to enable them, are described below

and on the following page.

REGISTERED

In registered mode the output pin associated with an individual

OLMC is driven by the Q output of that OLMC’s D-type flip-flop.

Logic polarity of the output signal at the pin may be selected by

specifying that the output buffer drive either true (active high) or

inverted (active low). Output tri-state control is available as an in-

dividual product-term for each OLMC, and can therefore be defined

by a logic equation. The D flip-flop’s /Q output is fed back into the

AND array, with both the true and complement of the feedback

available as inputs to the AND array.

NOTE: In registered mode, the feedback is from the /Q output of

the register, and not from the pin; therefore, a pin defined as reg-

istered is an output only, and cannot be used for dynamic

I/O, as can the combinatorial pins.

COMBINATORIAL I/O

In combinatorial mode the pin associated with an individual OLMC

is driven by the output of the sum term gate. Logic polarity of the

output signal at the pin may be selected by specifying that the output

buffer drive either true (active high) or inverted (active low). Out-

put tri-state control is available as an individual product-term for

each output, and may be individually set by the compiler as either

“on” (dedicated output), “off” (dedicated input), or “product-term

driven” (dynamic I/O). Feedback into the AND array is from the pin

side of the output enable buffer. Both polarities (true and inverted)

of the pin are fed back into the AND array.

The GAL22V10 has a variable number of product terms per OLMC.

Of the ten available OLMCs, two OLMCs have access to eight

product terms (pins 14 and 23, DIP pinout), two have ten product

terms (pins 15 and 22), two have twelve product terms (pins 16 and

21), two have fourteen product terms (pins 17 and 20), and two

OLMCs have sixteen product terms (pins 18 and 19). In addition

to the product terms available for logic, each OLMC has an addi-

tional product-term dedicated to output enable control.

The output polarity of each OLMC can be individually programmed

to be true or inverting, in either combinatorial or registered mode.

This allows each output to be individually configured as either active

high or active low.

The GAL22V10 has a product term for Asynchronous Reset (AR)

and a product term for Synchronous Preset (SP). These two prod-

uct terms are common to all registered OLMCs. The Asynchronous

Reset sets all registers to zero any time this dedicated product term

is asserted. The Synchronous Preset sets all registers to a logic

one on the rising edge of the next clock pulse after this product term

is asserted.

NOTE: The AR and SP product terms will force the Q output of the

flip-flop into the same state regardless of the polarity of the output.

Therefore, a reset operation, which sets the register output to a zero,

may result in either a high or low at the output pin, depending on

the pin polarity chosen.

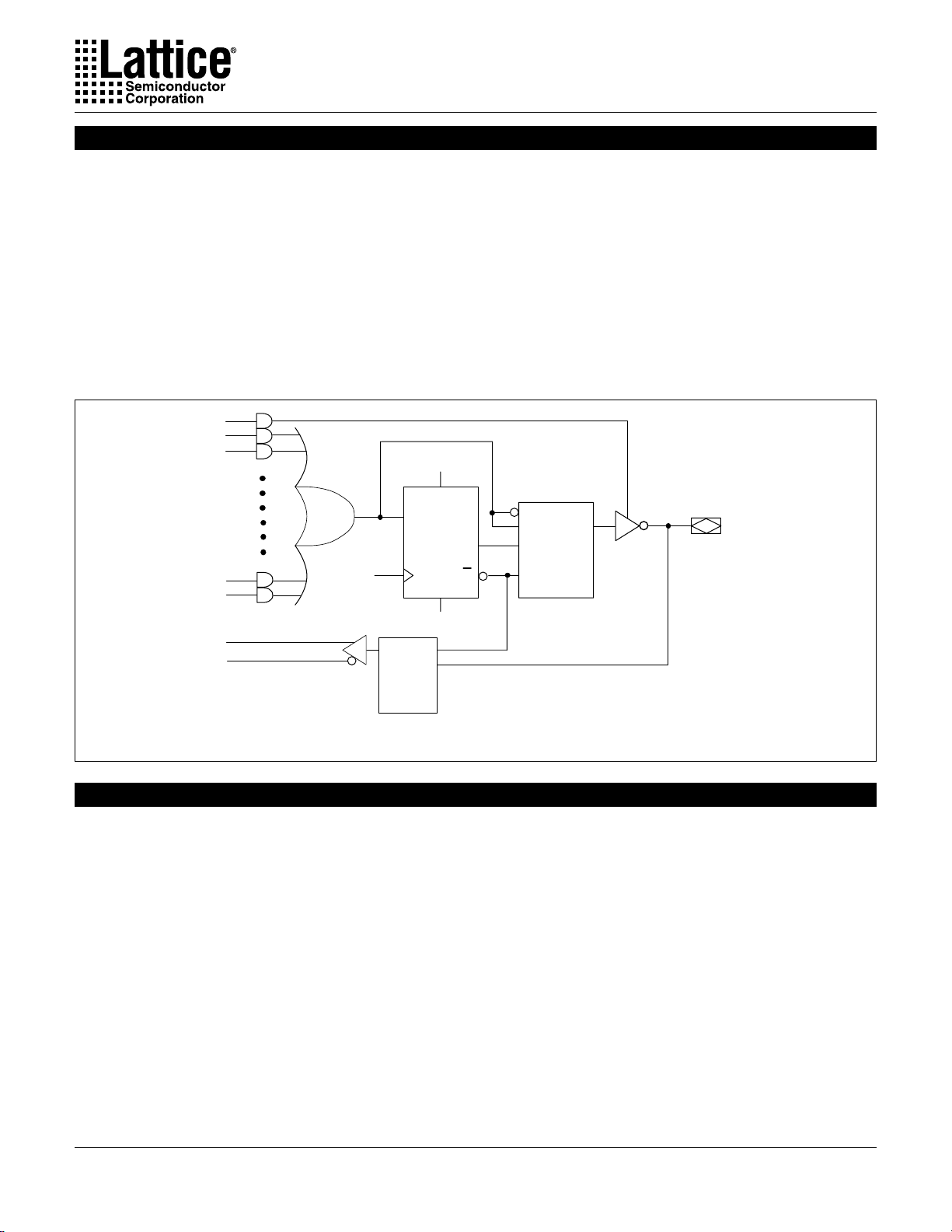

AR

SP

D

Q

QCLK

4 TO 1

MUX

2 TO 1

MUX

Output Logic Macrocell (OLMC)

Output Logic Macrocell Configurations

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件