Datasheet 搜索 > 时钟信号器件 > Integrated Device Technology(艾迪悌) > ICS954101DFLFT 数据手册 > ICS954101DFLFT 数据手册 6/17 页

器件3D模型

器件3D模型¥ 0

ICS954101DFLFT 数据手册 - Integrated Device Technology(艾迪悌)

制造商:

Integrated Device Technology(艾迪悌)

分类:

时钟信号器件

封装:

SSOP

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

ICS954101DFLFT数据手册

Page:

of 17 Go

若手册格式错乱,请下载阅览PDF原文件

6

Integrated

Circuit

Systems, Inc.

ICS954101

0815G—12/02/08

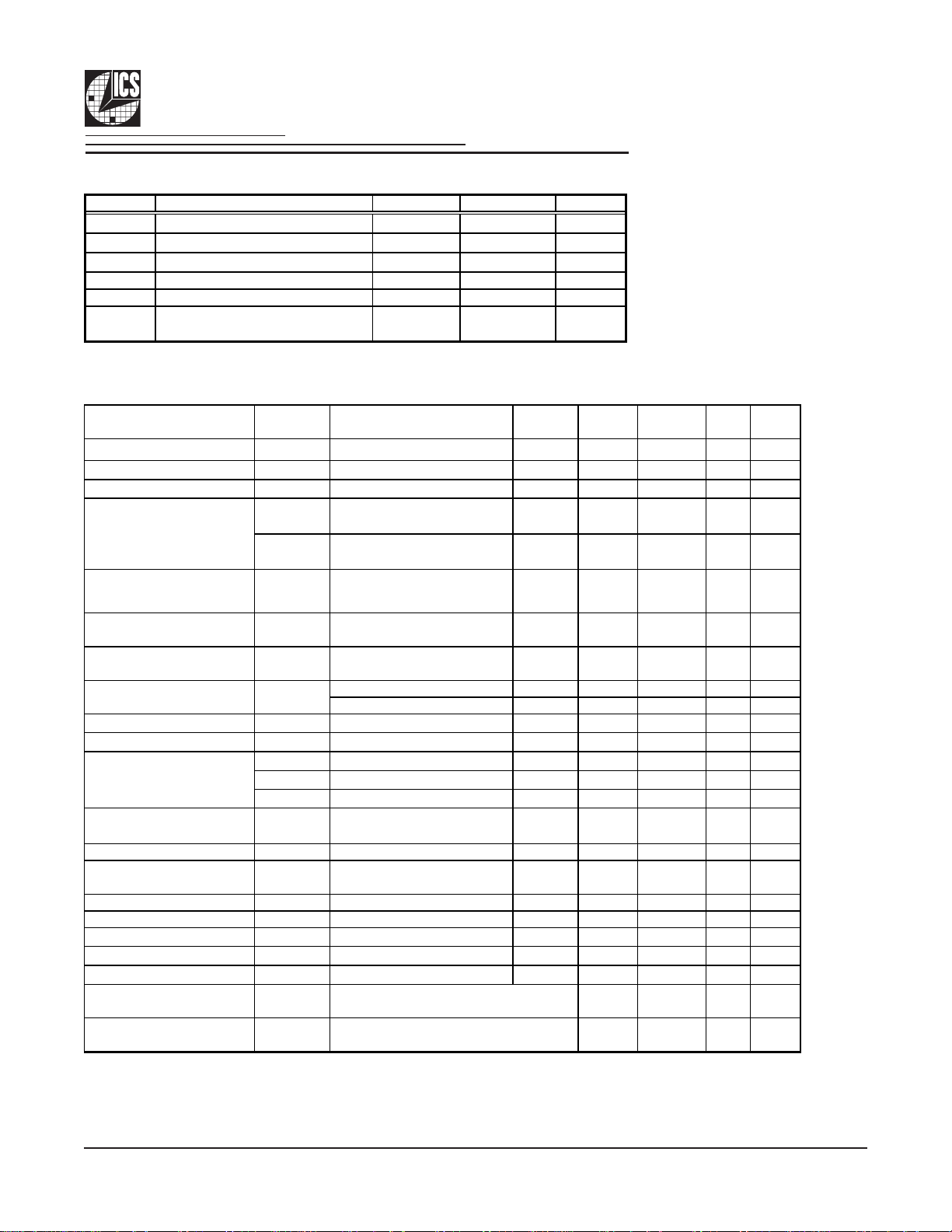

Absolute Max

Symbol Parameter Min Max Units

VDD_A 3.3V Core Supply Voltage V

DD

+ 0.5V V

VDD_In 3.3V Logic Input Supply Voltage GND - 0.5 V

DD

+ 0.5V V

Ts Storage Temperature -65 150

°

C

Tambient Ambient Operating Temp 0 70 °C

Tcase Case Temperature 115 °C

ESD prot

Input E

S

D protection

human body model

2000 V

Electrical Characteristics - Input/Supply/Common Output Parameters

T

A

= 0 - 70°C; Supply Voltage V

DD

= 3.3 V +/-5%

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS NOTES

Input High Voltage V

IH

3.3 V +/-5% 2 V

DD

+ 0.3 V

Input Low Voltage V

IL

3.3 V +/-5% V

SS

- 0.3 0.8 V

Input High Current I

IH

V

IN

= V

D

D

-5 5 uA

I

IL1

V

IN

= 0 V; Inputs with no pull-

up resistors

-5 uA

I

IL2

V

IN

= 0 V; Inputs with pull-up

resistors

-200 uA

Low Threshold Input High

Voltage

V

IH_FS

3.3 V +/-5% 0.7 V

DD

+ 0.3 V

Low Threshold Input Low

Volta

g

e

V

IL_FS

3.3 V +/-5% V

SS

- 0.3 0.35 V

Operating Supply Current I

DD3. 3OP

3.3 V +/-5%, Full Load 350 500 mA

all diff pairs driven 70 mA

all differential pairs tri-stated 12 mA

Input Frequency

3

F

i

V

DD

= 3.3 V 14.31818 MHz 3

Pin Inductance

1

L

p

in

7nH1

C

IN

Logic Inputs 5 pF 1

C

OUT

Output pin capacitance 6 pF 1

C

INX

X1 & X2 pins 5 pF 1

Clk Stabilization

1,2

T

STAB

From V

DD

Power-Up or de-

assertion of PD# to 1st clock

1.8 ms 1,2

Modulation Frequency Trian

g

ular Modulation 30 33 kHz 1

Tdrive_PD#

CPU output enable after

PD# de-assertion

300 us 1

Tfall_Pd# PD# fall time of 5 ns 1

Trise_Pd# PD# rise time of 5 ns 2

SMBus Voltage V

D

D

2.7 5.5 V 1

Low-level Output Voltage V

OLSMBUS

@ I

PULLUP

0.4 V 1

C

urrent sinking at V

OL

= 0.4

V

I

PULLUP

4mA1

SCLK/SDATA

Clock/Data Rise Time

T

RI2C

(Max VIL - 0.15) to (Min VIH + 0.15) 1000 ns 1

SCLK/SDATA

Clock/Data Fall Time

T

FI 2C

(Min VIH + 0.15) to (Max VIL - 0.15) 300 ns 1

1

Guaranteed by desi

g

n and characterization, not 100% tested in production.

2

See timin

g

dia

g

rams for timin

g

requirements.

3

Input frequency should be measured at the REF output pin and tuned to ideal 14.31818MHz to meet ppm accuracy on PLL outputs.

Input Low Current

Powerdown Current I

DD3.3PD

Input Capacitance

1

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件