Datasheet 搜索 > Integrated Device Technology(艾迪悌) > IDT7006S35JB 数据手册 > IDT7006S35JB 数据手册 6/20 页

¥ 0

IDT7006S35JB 数据手册 - Integrated Device Technology(艾迪悌)

制造商:

Integrated Device Technology(艾迪悌)

描述:

高速16K ×8双端口静态RAM HIGH-SPEED 16K x 8 DUAL-PORT STATIC RAM

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

IDT7006S35JB数据手册

Page:

of 20 Go

若手册格式错乱,请下载阅览PDF原文件

6.07 6

IDT7006S/L

HIGH-SPEED 16K x 8 DUAL-PORT STATIC RAM MILITARY AND COMMERCIAL TEMPERATURE RANGES

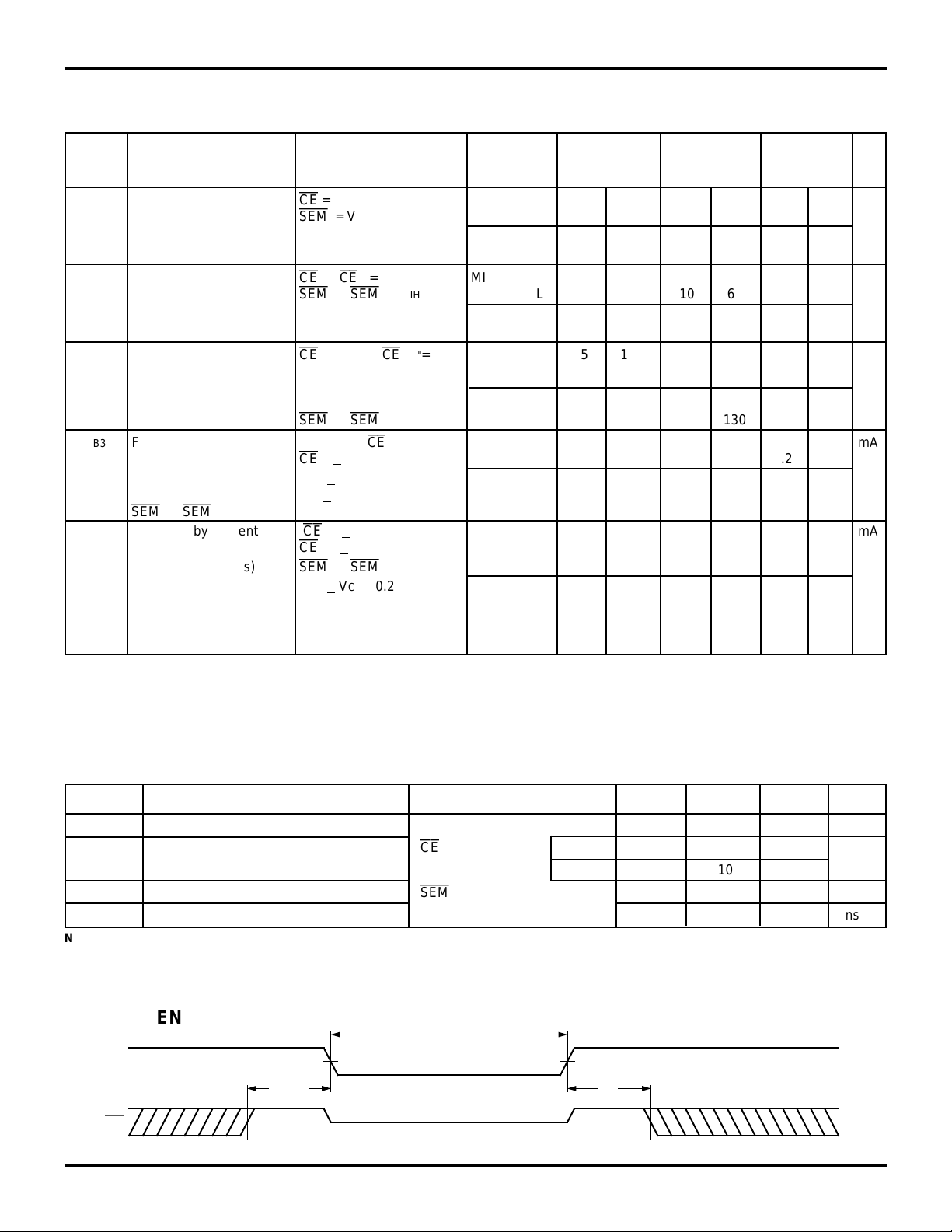

DC ELECTRICAL CHARACTERISTICS OVER THE

OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE

(1)

(Cont'd.) (VCC = 5.0V ± 10%)

7006X35 7006X55 7006X70

Test Mil Only

Symbol Parameter Condition Version Typ.

(2)

Max. Typ.

(2)

Max. Typ.

(2)

Max. Unit

I

CC Dynamic Operating

CE

= VIL, Outputs Open MIL. S 150 300 150 300 140 300 mA

Current

SEM

= V

IH L 140 250 140 250 130 250

(Both Ports Active) f = f

MAX

(3)

COM’L. S 150 250 150 250 — —

L 140 210 140 210 — —

I

SB1 Standby Current

CE

L =

CE

R = VIH MIL. S 13 80 13 80 10 80 mA

(Both Ports — TTL

SEM

R =

SEM

L = VIH L10 65 10 65 8 65

Level Inputs) f = f

MAX

(3)

COM’L. S 13 60 13 60 — —

L10 50 10 50 — —

I

SB2 Standby Current

CE

"A"=VIL and

CE

L"B"=VIH

(5)

MIL. S 85 190 85 190 80 190 mA

(One Port — TTL Active Port Outputs Open, L 75 160 75 160 70 160

Level Inputs) f = f

MAX

(3)

COM’L. S 85 155 85 155 — —

SEM

R =

SEM

L = VIH L 75 130 75 130 — —

I

SB3 Full Standby Current Both Ports

CE

L and MIL. S 1.0 30 1.0 30 1.0 30 mA

(Both Ports — All

CE

R > VCC - 0.2V L 0.2 10 0.2 10 0.2 10

CMOS Level Inputs) V

IN > VCC - 0.2V or COM’L. S 1.0 15 1.0 15 — —

V

IN < 0.2V, f = 0

(4)

L 0.2 5 0.2 5 — —

SEM

R =

SEM

L≥ VCC-0.2V

I

SB4 Full Standby Current

CE

"A" < 0.2V and MIL. S 80 175 80 175 75 175 mA

(One Port — All

CE

"B" > VCC - 0.2V

(5)

CMOS Level Inputs)

SEM

R =

SEM

L≥ VCC - 0.2V L 70 150 70 150 65 150

V

IN > VCC - 0.2V or COM’L. S 80 135 80 135 — —

V

IN < 0.2V

Active Port Outputs Open, L 70 110 70 110 — —

f = f

MAX

(3)

DATA RETENTION CHARACTERISTICS OVER ALL TEMPERATURE RANGES (L Version Only)

(VLC = 0.2V, VHC = VCC - 0.2V)

(4)

Symbol Parameter Test Condition Min. Typ.

(1)

Max. Unit

V

DR VCC for Data Retention VCC = 2V 2.0 — — V

I

CCDR Data Retention Current

CE

≥ VHC MIL. — 100 4000 µA

V

IN ≥ VHC or ≤ VLC COM’L. — 100 1500

t

CDR

(3)

Chip Deselect to Data Retention Time

SEM

≥ VHC 0——ns

t

R

(3)

Operation Recovery Time tRC

(2)

——ns

NOTES: 2739 tbl 11

1. TA = +25°C, VCC = 2V, and are not production tested.

2. t

RC = Read Cycle Time

3. This parameter is guaranteed by characterization, but are not production tested.

4. At Vcc = 2V input leakages are undefined

DATA RETENTION MODE

V

CC

CE

2739 drw 05

4.5V

t

CDR

t

R

V

IH

V

DR

V

IH

4.5V

V

DR

2V

≥

DATA RETENTION WAVEFORM

NOTES: 2739 tbl 10

1. "X" in part numbers indicates power rating (S or L).

2. V

CC = 5V, TA = +25°C, and are not production tested. ICC DC =120mA (typ).

3. At f = fMAX, address and I/O'S are cycling at the maximum frequency read cycle of 1/tRC, and using “AC Test Conditions” of input levels of GND to 3V.

4. f = 0 means no address or control lines change.

5. Port "A" may be either left or right port. Port "B"is the opposite from port "A".

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件