Datasheet 搜索 > Renesas Electronics(瑞萨电子) > ISL29030IROZ-T7R5430 数据手册 > ISL29030IROZ-T7R5430 数据手册 5/17 页

¥ 0

ISL29030IROZ-T7R5430 数据手册 - Renesas Electronics(瑞萨电子)

制造商:

Renesas Electronics(瑞萨电子)

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

ISL29030IROZ-T7R5430数据手册

Page:

of 17 Go

若手册格式错乱,请下载阅览PDF原文件

ISL29030

5

FN6872.1

November 12, 2012

C

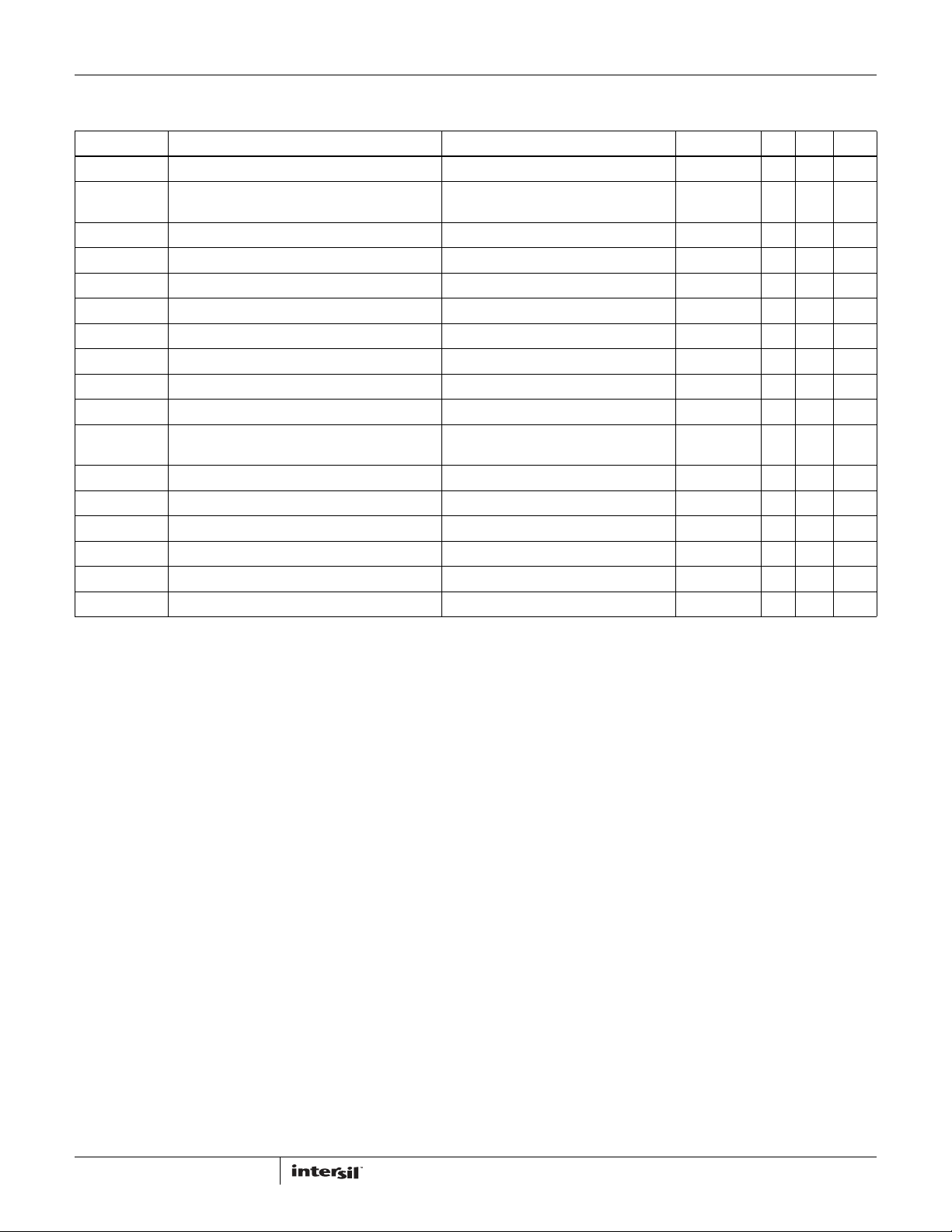

i

Capacitance for each SDA and SCL Pin 10 pF

t

HD:STA

Hold Time (Repeated) START Condition After this period, the first clock pulse is

generated

600 ns

t

LOW

LOW Period of the SCL Clock Measured at the 30% of VDD crossing 1300 ns

t

HIGH

HIGH period of the SCL Clock 600 ns

t

SU:STA

Set-up Time for a Repeated START Condition 600 ns

t

HD:DAT

Data Hold Time 30 ns

t

SU:DAT

Data Set-up Time 100 ns

t

R

Rise Time of both SDA and SCL Signals (Note 12) 20 + 0.1xC

b

ns

t

F

Fall Time of both SDA and SCL Signals (Note 12) 20 + 0.1xC

b

ns

t

SU:STO

Set-up Time for STOP Condition 600 ns

t

BUF

Bus Free Time Between a STOP and START

Condition

1300 ns

C

b

Capacitive Load for Each Bus Line 400 pF

R

pull-up

SDA and SCL system bus pull-up resistor Maximum is determined by t

R

and t

F

1kΩ

t

VD;DAT

Data Valid Time 0.9 µs

t

VD:ACK

Data Valid Acknowledge Time 0.9 µs

V

nL

Noise Margin at the LOW Level 0.1VDD V

V

nH

Noise Margin at the HIGH Level 0.2VDD V

NOTES:

11. I

2

C limits are based on design/simulation and are not production tested.

12. C

b

is the capacitance of the bus in pF.

I

2

C Electrical Specifications For SCL and SDA unless otherwise noted, V

DD

= 3V, T

A

= +25°C, R

EXT

= 499kΩ 1% tolerance

(Note 11). (Continued)

PARAMETER DESCRIPTION CONDITION MIN TYP MAX UNIT

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件