Datasheet 搜索 > CPLD芯片 > Lattice Semiconductor(莱迪思) > ISPGAL22V10AV-75LNNI 数据手册 > ISPGAL22V10AV-75LNNI 数据手册 6/19 页

器件3D模型

器件3D模型¥ 0

ISPGAL22V10AV-75LNNI 数据手册 - Lattice Semiconductor(莱迪思)

制造商:

Lattice Semiconductor(莱迪思)

分类:

CPLD芯片

封装:

QFN-32

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

ISPGAL22V10AV-75LNNI数据手册

Page:

of 19 Go

若手册格式错乱,请下载阅览PDF原文件

Lattice Semiconductor ispGAL22V10AV/B/C Data Sheet

4

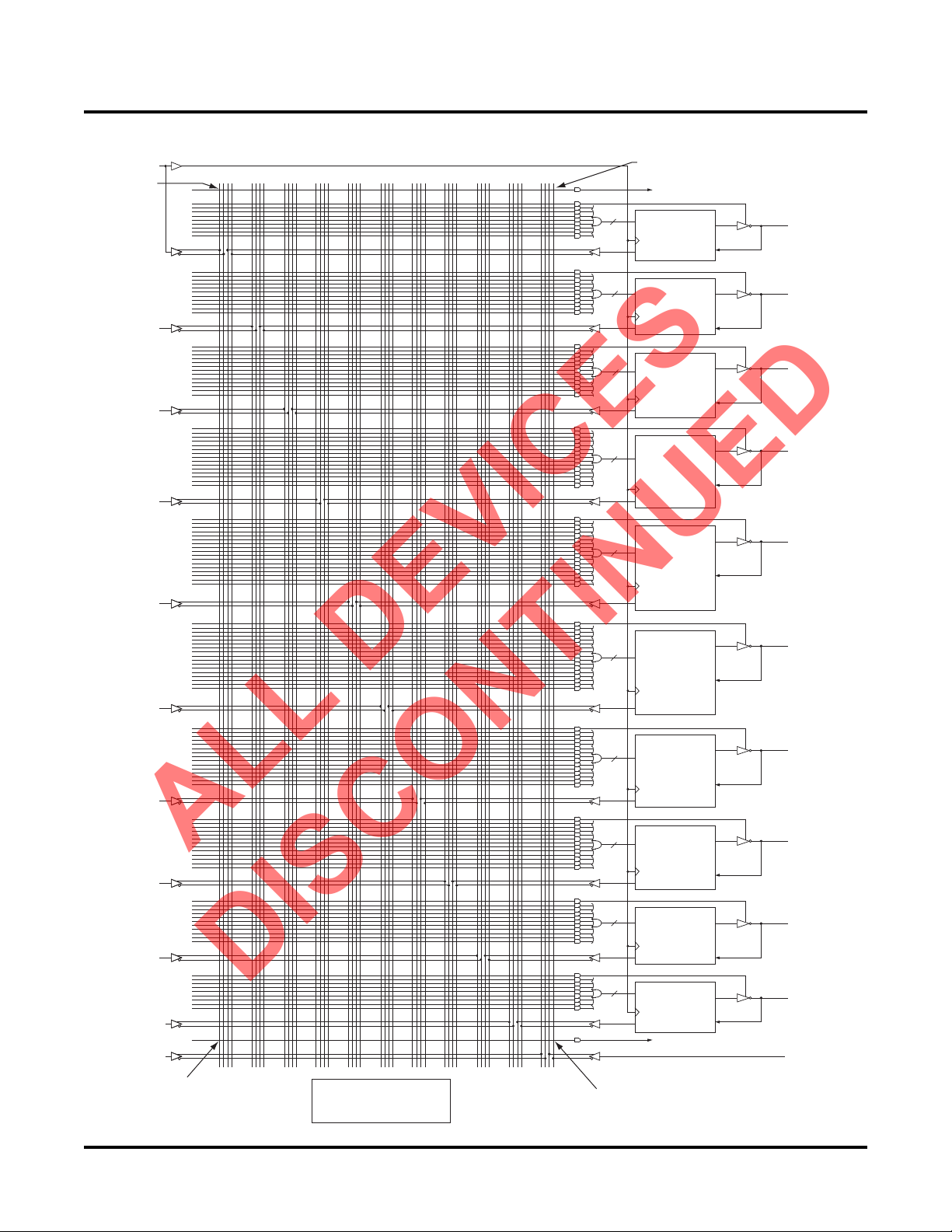

Figure 5. Logic Diagram/JEDEC Fuse Map – PLCC & (QFN/QFNS) Package Pinout

2 (30)

26 (25)

OLMC

S1, S0 = 5810, 5811

SR = 5832

OD = 5833

3 (31)

ASYNCHRONOUS RESET

(TO ALL REGISTERS)

0

JEDEC

Fuse #0

4 8 12 16 20 24 28 32 36 40

SYNCHRONOUS PRESET

(TO ALL REGISTERS)

12 (9)

27 (26)

S1, S0 = 5808, 5809

SR = 5830

OD = 5831

25 (24)

OLMC

S1, S0 = 5812, 5813

SR = 5834

OD = 5835

4 (32)

5 (1)

6 (2)

24 (23)

OLMC

S1, S0 = 5814, 5815

SR = 5836

OD = 5837

23 (22)

OLMC

S1, S0 = 5816, 5817

SR = 5838

OD = 5839

21 (19)

OLMC

S1, S0 = 5818, 5819

SR = 5840

OD = 5841

20 (18)

OLMC

S1, S0 = 5820, 5821

SR = 5842

OD = 5843

OLMC

S1, S0 = 5822, 5823

SR = 5844

OD = 5845

10 (7)

19 (17)

18 (16)

OLMC

S1, S0 = 5824, 5825

SR = 5846

OD = 5847

11 (8)

17 (15)

OLMC

S1, S0 = 5826, 5827

SR = 5848

OD = 5849

9 (6)

7 (3)

13 (10) 16 (14)

8

10

14

16

12

12

16

14

10

8

OLMC

S1, S0 = Arch Control Bits

SR = Slew Rate Bit

OD = Open Drain Bit

JEDEC Fuse #131

JEDEC

Fuse #5676

JEDEC Fuse #5807

ALL DEVICES

DISCONTINUED

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件