Datasheet 搜索 > 微控制器 > TI(德州仪器) > LM3S6965-IQC50-A2T 数据手册 > LM3S6965-IQC50-A2T 数据手册 548/761 页

器件3D模型

器件3D模型¥ 249.327

LM3S6965-IQC50-A2T 数据手册 - TI(德州仪器)

制造商:

TI(德州仪器)

分类:

微控制器

封装:

LQFP-100

描述:

的Stellaris LM3S6965微控制器 Stellaris LM3S6965 Microcontroller

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P160P172P336P396P433P476P514P551P599P612P650Hot

典型应用电路图在P47P610

原理图在P44P45P54P55P56P160P240P260P293P335P372P395

封装尺寸在P52P749P750P752P753P754P756P757P759P760

型号编码规则在P747

标记信息在P747P757P758

封装信息在P747P751P752P756P757P758P759P760

功能描述在P95P161P172P241P260P292P336P372P397P434P476P515

技术参数、封装参数在P699P701P702P703P705

应用领域在P44P58P179P761

电气规格在P52P700P702P704P706P708P710P712P714P716

导航目录

LM3S6965-IQC50-A2T数据手册

Page:

of 761 Go

若手册格式错乱,请下载阅览PDF原文件

Register 15: I

2

C Slave Masked Interrupt Status (I2CSMIS), offset 0x814

This register specifies whether an interrupt was signaled.

I2C Slave Masked Interrupt Status (I2CSMIS)

I2C 0 base: 0x4002.0000

I2C 1 base: 0x4002.1000

Offset 0x814

Type RO, reset 0x0000.0000

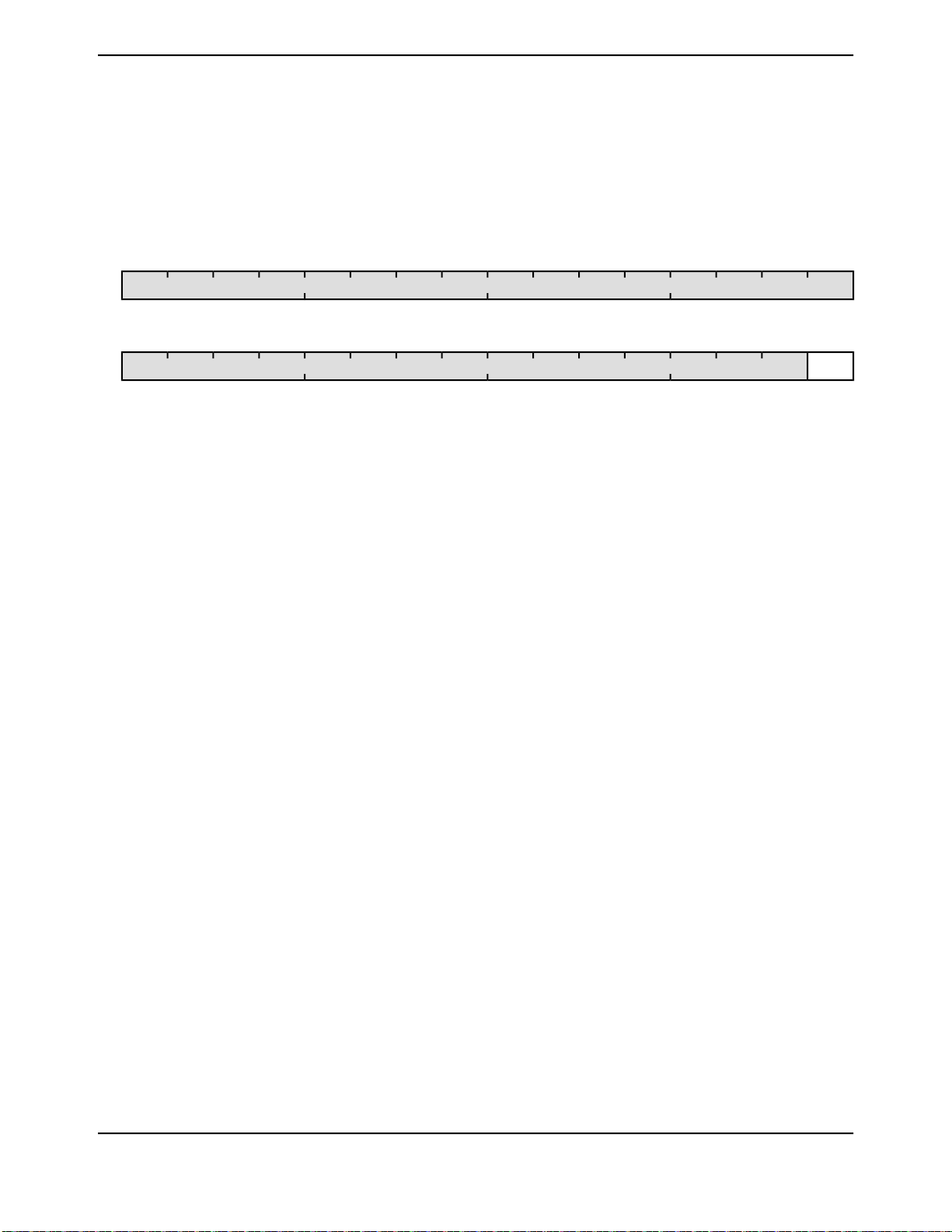

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

0123456789101112131415

DATAMISreserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x00ROreserved31:1

Data Masked Interrupt Status

This bit specifies the interrupt state for data received and data requested

(after masking) of the I

2

C slave block. If set, an interrupt was signaled;

otherwise, an interrupt has not been generated since the bit was last

cleared.

0RODATAMIS0

July 15, 2014548

Texas Instruments-Production Data

Inter-Integrated Circuit (I

2

C) Interface

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件