Datasheet 搜索 > 接口隔离器 > Maxim Integrated(美信) > MAX14850AEE+T 数据手册 > MAX14850AEE+T 数据手册 6/17 页

器件3D模型

器件3D模型¥ 15.521

MAX14850AEE+T 数据手册 - Maxim Integrated(美信)

制造商:

Maxim Integrated(美信)

分类:

接口隔离器

封装:

SSOP-16

描述:

数字隔离器 Six Channel 600vrms Digital Isolator

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P11P12Hot

典型应用电路图在P1P12P15P16

封装尺寸在P16

型号编码规则在P1P16

封装信息在P16

功能描述在P1

技术参数、封装参数在P6

应用领域在P1P14

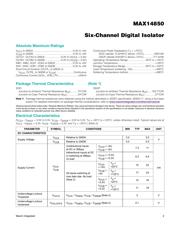

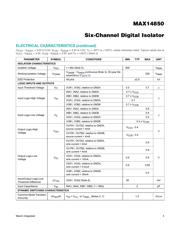

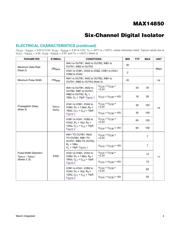

电气规格在P3P4P5P13

导航目录

MAX14850AEE+T数据手册

Page:

of 17 Go

若手册格式错乱,请下载阅览PDF原文件

MAX14850

Six-Channel Digital Isolator

6Maxim Integrated

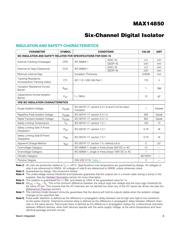

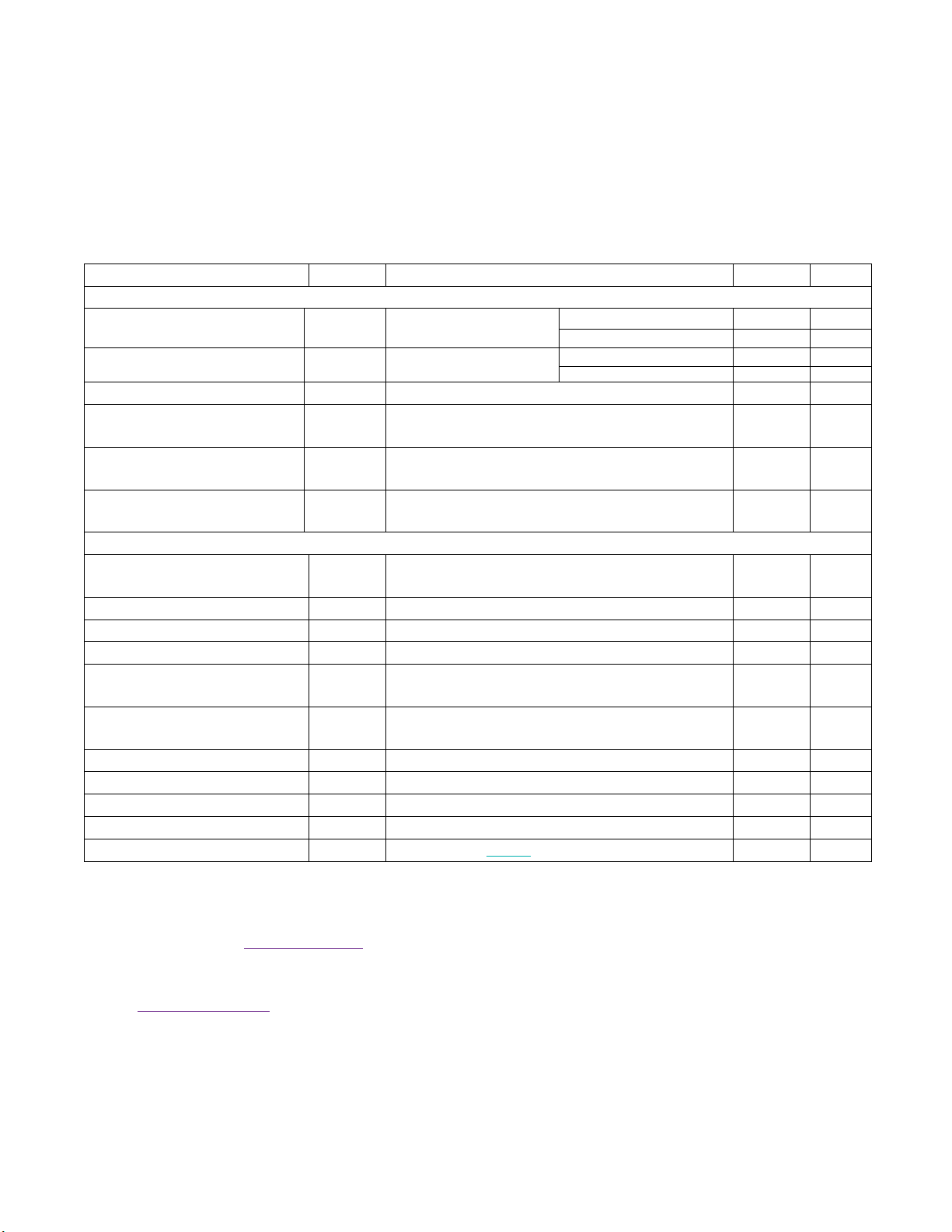

INSULATION AND SAFETY CHARACTERISTICS

Note 2: All units are production tested at T

A

= +25°C. Specifications over temperature are guaranteed by design. All voltages of

side A are referenced to GNDA. All voltages of side B are referenced to GNDB, unless otherwise noted.

Note 3: Guaranteed by design. Not production tested.

Note 4: The undervoltage lockout threshold and hysteresis guarantee that the outputs are in a known state during a slump in the

supplies. See the Detailed Description section for more information.

Note 5: The isolation is guaranteed for t = 60s, and tested at 120% of the guaranteed value for 1s.

Note 6: DV

TOL

= V

OL

– V

IL

. This is the minimum difference between the output logic-low voltage and the input logic threshold for

the same I/O pin. This ensures that the I/O channels are not latched low when any of the I/O inputs are driven low (see the

Bidirectional Channels section).

Note 7: The common-mode transient immunity guarantees that the device will hold its outputs stable when the isolation voltage

changes at the specified rate.

Note 8: Pulse-width distortion is defined as the difference in propagation delay between low-to-high and high-to-low transitions

on the same channel. Channel-to-channel skew is defined as the difference in propagation delay between different chan-

nels on the same device. Part-to-part skew is defined as the difference in propagation delays (for unidirectional channels)

between different devices, when both devices operate with the same supply voltage, at the same temperature and have

identical package and test circuits.

PARAMETER SYMBOL CONDITIONS VALUE UNIT

IEC INSULATION AND SAFETY RELATED FOR SPECIFICATIONS FOR SOIC-16

External Tracking (Creepage) CPG IEC 60664-1

SOIC-16 4.2 mm

QSOP-16 3.81 mm

External Air Gap (Clearance) CLR IEC 60664-1

SOIC-16 4.2 mm

QSOP-16 3.81 mm

Minimum Internal Gap Insulation Thickness 0.0026 mm

Tracking Resistance

(Comparative Tracking Index)

CTI IEC 112 / VDE 030 Part 1 175 V

Insulation Resistance Across

Barrier

R

ISO

1

GI

Capacitance Across Isolation

Barrier

C

IO

f = 1MHz 12 pF

VDE IEC INSULATION CHARACTERISTICS

Surge Isolation Voltage V

IOSM

IEC 60747-17, section 5.3.1.6 and 5.4.6 for basic

insulation

1 kVpeak

Repetitive Peak Isolation Voltage V

IORM

IEC 60747-17, section 5.3.1.3 282 Vpeak

Rated Transient Isolation Voltage V

IOTM

IEC 60747-17, section 5.3.1.4 850 Vpeak

Safety Limiting Temperature T

S

IEC 60747-17, section 7.2.1 150

NC

Safety Limiting Side A Power

Dissipation

P

SA

IEC 60747-17, section 7.2.1 0.75 W

Safety Limiting Side B Power

Dissipation

P

SB

IEC 60747-17, section 7.2.1 0.75 W

Apparent Charge Method q

pd

IEC 60747-17, section 7.4, method a & b 5 pC

Overvoltage Category IEC 60664-1, single or three phase 50V DC or AC I,II —

Overvoltage Category IEC 60664-1, single or three phase 100V DC or AC I —

Climatic Category 40/125/21 —

Pollution Degree DIN VDE 0110, Table 1 2 —

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件