Datasheet 搜索 > 逻辑控制器 > ON Semiconductor(安森美) > MC14557BCP 数据手册 > MC14557BCP 数据手册 5/8 页

器件3D模型

器件3D模型¥ 0

MC14557BCP 数据手册 - ON Semiconductor(安森美)

制造商:

ON Semiconductor(安森美)

分类:

逻辑控制器

封装:

PDIP

描述:

1到64位可变长度的移位寄存器 1-to-64 Bit Variable Length Shift Register

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

MC14557BCP数据手册

Page:

of 8 Go

若手册格式错乱,请下载阅览PDF原文件

MC14557B

http://onsemi.com

5

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

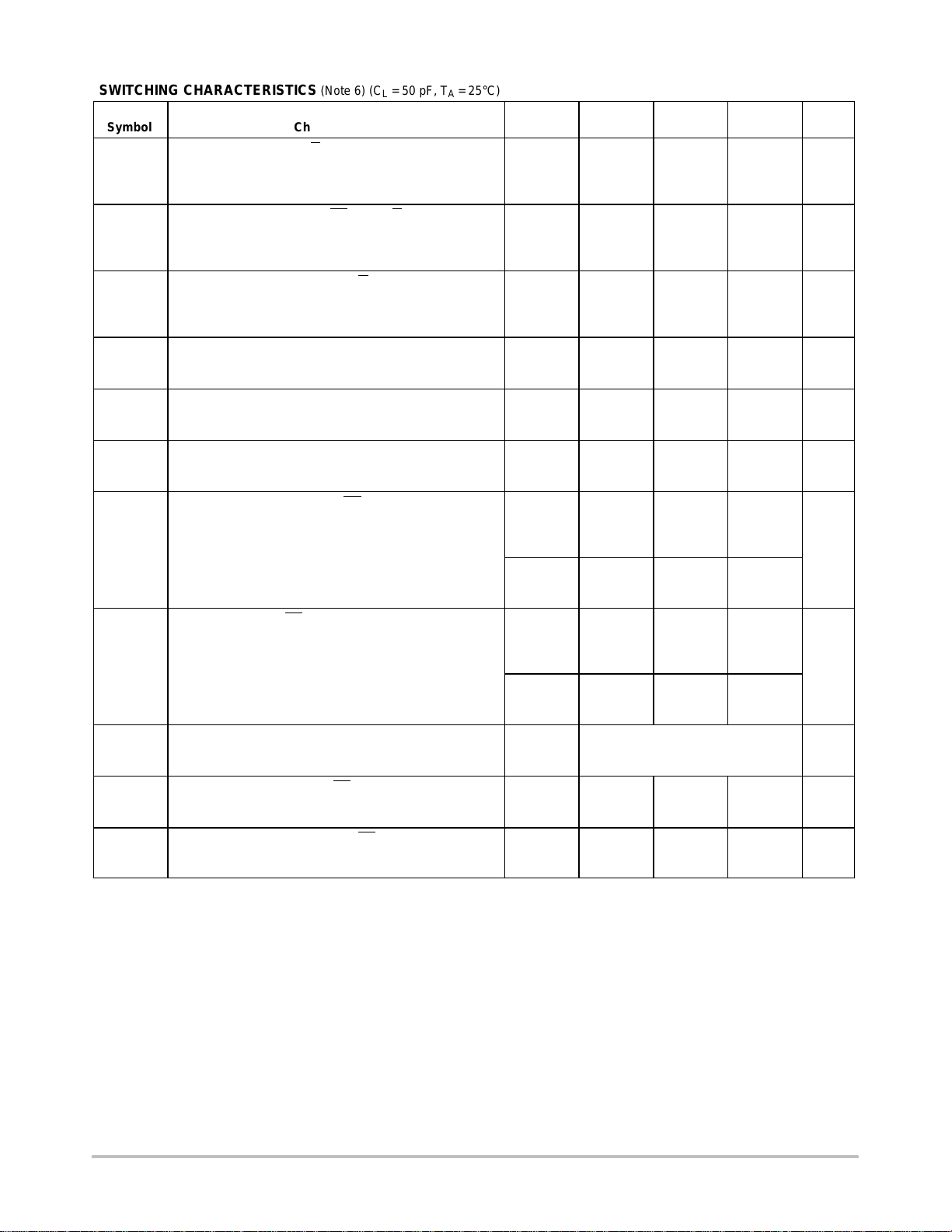

SWITCHING CHARACTERISTICS (Note 6) (C

L

= 50 pF, T

A

= 25°C)

Symbol

Characteristic V

DD

Min

Typ

(Note 7)

Max Unit

t

TLH

,

t

THL

Rise and Fall Time, Q or Q Output

t

TLH

, t

THL

= (1.5 ns/pF) C

L

+ 25 ns

t

TLH

, t

THL

= (0.75 ns/pF) C

L

+ 12.5 ns

t

TLH

, t

THL

= (0.55 ns/pF) C

L

+ 9.5 ns

5

10

15

−

−

−

100

50

40

200

100

80

ns

t

PLH

,

t

PHL

Propagation Delay, Clock or CE to Q or Q

t

PLH

, t

PHL

= (1.7 ns/pF) C

L

+ 215 ns

t

PLH

, t

PHL

= (0.66 ns/pF) C

L

+ 97 ns

t

PLH

, t

PHL

= (0.5 ns/pF) C

L

+ 65 ns

5

10

15

−

−

−

300

130

90

600

260

180

ns

t

PLH

,

t

PHL

Propagation Delay, Reset to Q or Q

t

PLH

, t

PHL

= (1.7 ns/pF) C

L

+ 215 ns

t

PLH

, t

PHL

= (0.66 ns/pF) C

L

+ 97 ns

t

PLH

, t

PHL

= (0.5 ns/pF) C

L

+ 70 ns

5

10

15

−

−

−

300

130

95

600

260

190

ns

t

WH(cl)

Pulse Width, Clock 5

10

15

200

100

75

95

45

35

−

−

−

ns

t

WH(rst)

Pulse Width, Reset 5

10

15

300

140

100

150

70

50

−

−

−

ns

f

cl

Clock Frequency (50% Duty Cycle) 5

10

15

−

−

−

3.0

7.5

13.0

1.7

5.0

6.7

MHz

t

su

Setup Time, A or B to Clock or CE

Worst case condition: L1 = L2 = L4 = L8 =

L16 = L32 = V

SS

(Register Length = 1)

5

10

15

700

290

145

350

130

85

−

−

−

ns

Best case condition: L32 = V

DD

, L1 through L16 =

Don’t Care (Any register length from 33 to 64)

5

10

15

400

165

60

45

5

0

−

−

−

t

h

Hold Time, Clock or CE to A or B

Best case condition: L1 = L2 = L4 = L8 = L16 =

L32 = V

SS

(Register Length = 1)

5

10

15

200

100

10

–150

–60

–50

−

−

−

ns

Worst case condition: L32 = V

DD

, L1 through L16 =

Don’t Care (Any register length from 33 to 64)

5

10

15

400

185

85

50

25

22

−

−

−

t

r

,

t

f

Rise and Fall Time, Clock 5

10

15

No Limit

−

t

r

,

t

f

Rise and Fall Time, Reset or CE 5

10

15

−

−

−

−

−

−

15

5

4

s

t

rem

Removal Time, Reset to Clock or CE 5

10

15

160

80

70

80

40

35

−

−

−

ns

6. The formulas given are for the typical characteristics only at 25°C.

7. Data labelled “Typ” is not to be used for design purposes but is intended as an indication of the IC’s potential performance.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件