Datasheet 搜索 > ON Semiconductor(安森美) > ML6428CS1X 数据手册 > ML6428CS1X 数据手册 3/10 页

器件3D模型

器件3D模型¥ 3.124

ML6428CS1X 数据手册 - ON Semiconductor(安森美)

制造商:

ON Semiconductor(安森美)

封装:

SOIC-8

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

ML6428CS1X数据手册

Page:

of 10 Go

若手册格式错乱,请下载阅览PDF原文件

DATA SHEET ML6428

REV. 1C April 2004

3

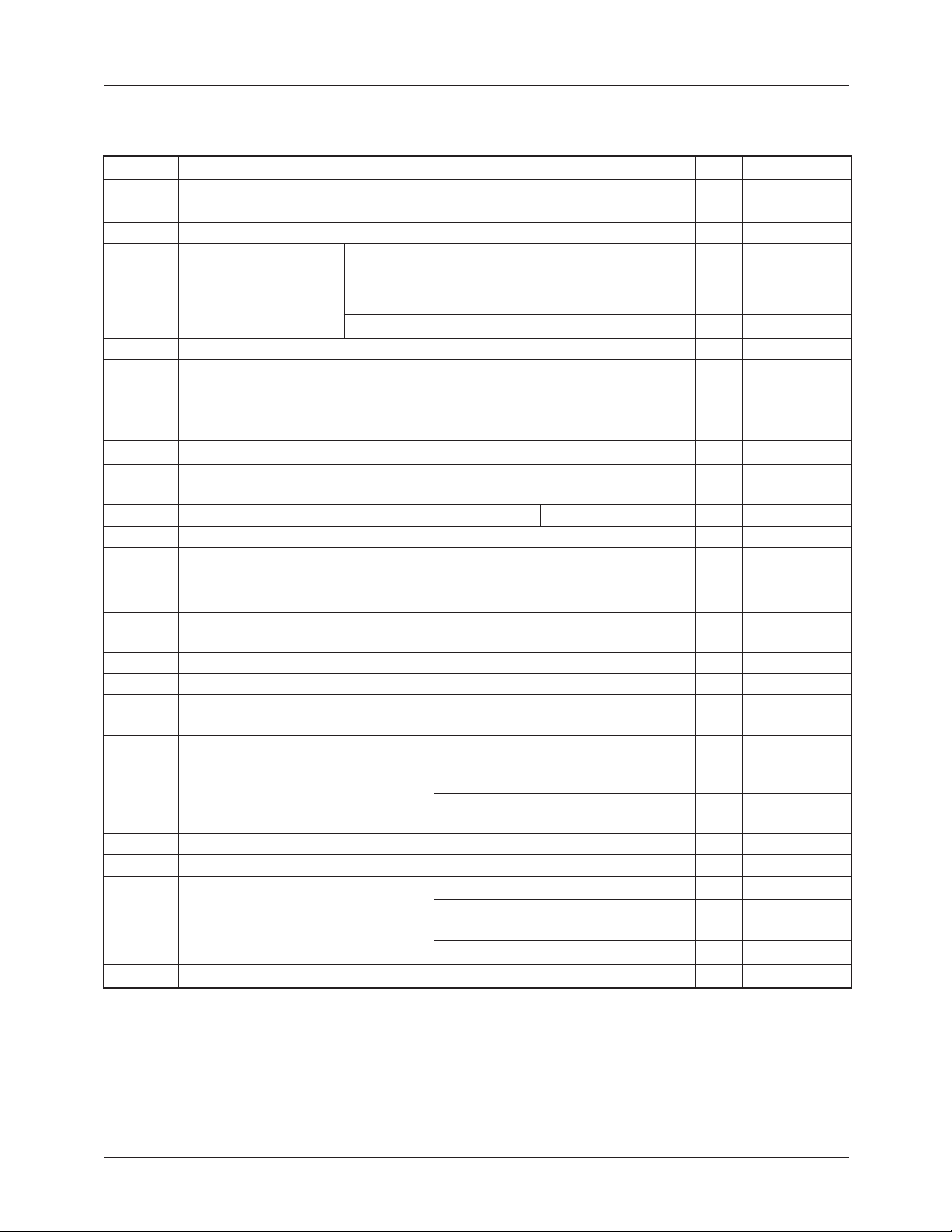

Electrical Table

Unless otherwise specified, V

CC

= 5V ±10%, All inputs AC coupled with 100nF, ML6428-1

outputs must be AC coupled, ML6428-2 outputs must be DC coupled. T

A

= Operating Temperature Range

1

Note

1: Limits are guaranteed by 100% testing, sampling, or correlation with worst case test conditions.

2: Sustained short circuit protection limited to 10 seconds.

Symbol Parameter Conditions Min. Typ. Max. Units

ICC Supply Current No Load (VCC = 5.0V) 52 80 mA

AV Low Frequency Gain (All Channels) VIN = 100mVP-P at 300KHz 5.34 6.0 6.65 dB

C DC Output Level (During Sync) Sync Present on Y 1.7 1.9 2.3 V

Y Sync Output Level ML6428-1 Sync Present on Y 0.7 0.9 1.3 V

ML6428-2 Sync Present on Y 0.35 0.54 0.95 V

Y+C Sync Output

Level

ML6428-1 Sync Present on Y 0.7 0.92 1.3 V

ML6428-2 Sync Present on Y 0.35 0.48 0.95 V

tCLAMP Clamp Response Time (Y Channel) Settled to Within 10mV 2 ms

f1dB -1dB Bandwidth (Flatness)

(All Channels)

4.0 4.8 MHz

fC -3dB Bandwidth (Flatness)

(All Channels)

6.7 MHz

0.8fC 0.8 x fC Attenuation (Y, C) 1.5 dB

fSB Stopband Rejection (All Channels) fIN = 27MHz to 100MHz worst

case

–42 –38 dB

Vi Input Signal Dynamic Range AC Coupled ML6428-1, -2 1.0 1.4 VP-P

NOISE Output Noise (All Channels) 25Hz to 50MHz 2.3 mVRMS

OS Peak Overshoot (All Channels) 2VP-P Output Pulse (loaded) 4.3 %

ISC Output Short Circuit Current

(All Channels)

VOUT C, Y, or CV (Note 2) 100 mA

CL Output Shunt Capacitance

(All Channels)

All Outputs 35 pF

dG Differential Gain (All Channels) All Outputs 0.4 %

d

Φ

Differential Phase (All Channels) All Outputs 0.4 °

THD Output Distortion (All Channels) VOUT = 1.8VP-P,

Y/C Out at 3.58MHz/4.43MHz

0.7 %

XTALK Crosstalk From C Input of 0.5VP-P at

3.58MHz/4.43MHz, to Y

Output

–55 dB

From Y Input of 0.4VP-P at

3.58MHz, to C Output

–58 dB

PSRR PSRR (All Channels) 0.5VP-P (100kHz) at VCC –49 dB

tpd Group Delay (All Channels) 100kHz 60 ns

∆

tpd Group Delay Deviation from

Flatness

(All Channels)

to 3.58MHz (NTSC) 4 ns

to 4.43MHz (PAL) without

peaking (see Figures 7 to 11)

7ns

to 10MHz 12 ns

tSKEW Skew Between Y & C Outputs 1 ns

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件