Datasheet 搜索 > Microchip(微芯) > PIC16F1827T-E/SS 数据手册 > PIC16F1827T-E/SS 数据手册 207/406 页

器件3D模型

器件3D模型¥ 0

PIC16F1827T-E/SS 数据手册 - Microchip(微芯)

制造商:

Microchip(微芯)

封装:

SSOP-20

描述:

18 /20/ 28引脚闪存单片机采用纳瓦XLP技术 18/20/28-Pin Flash Microcontrollers with nanoWatt XLP Technology

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P6P11P12P13P14P131P204P206P213P322Hot

典型应用电路图在P137P323

原理图在P10P16P52P63P73P97P131P135P139P154P158P164

封装尺寸在P384

标记信息在P383

封装信息在P383P385P386P390P391

功能描述在P315

技术参数、封装参数在P54P58P84P98P102P135P140P146P150P153P167P168

应用领域在P47P54P55P215P222

电气规格在P54P58P84P98P135P140P146P150P153P167P169P175

导航目录

PIC16F1827T-E/SS数据手册

Page:

of 406 Go

若手册格式错乱,请下载阅览PDF原文件

2011 Microchip Technology Inc. DS41391D-page 207

PIC16(L)F1826/27

24.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system

clock (F

OSC) for proper operation. Since FOSC is shut

down during Sleep mode, the Compare mode will not

function properly during Sleep.

24.2.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to

other locations with the use of the alternate pin function

registers, APFCON0 and APFCON1. To determine

which pins can be moved and what their default loca-

tions are upon a reset, see Section 12.1 “Alternate

Pin Function” for more information.

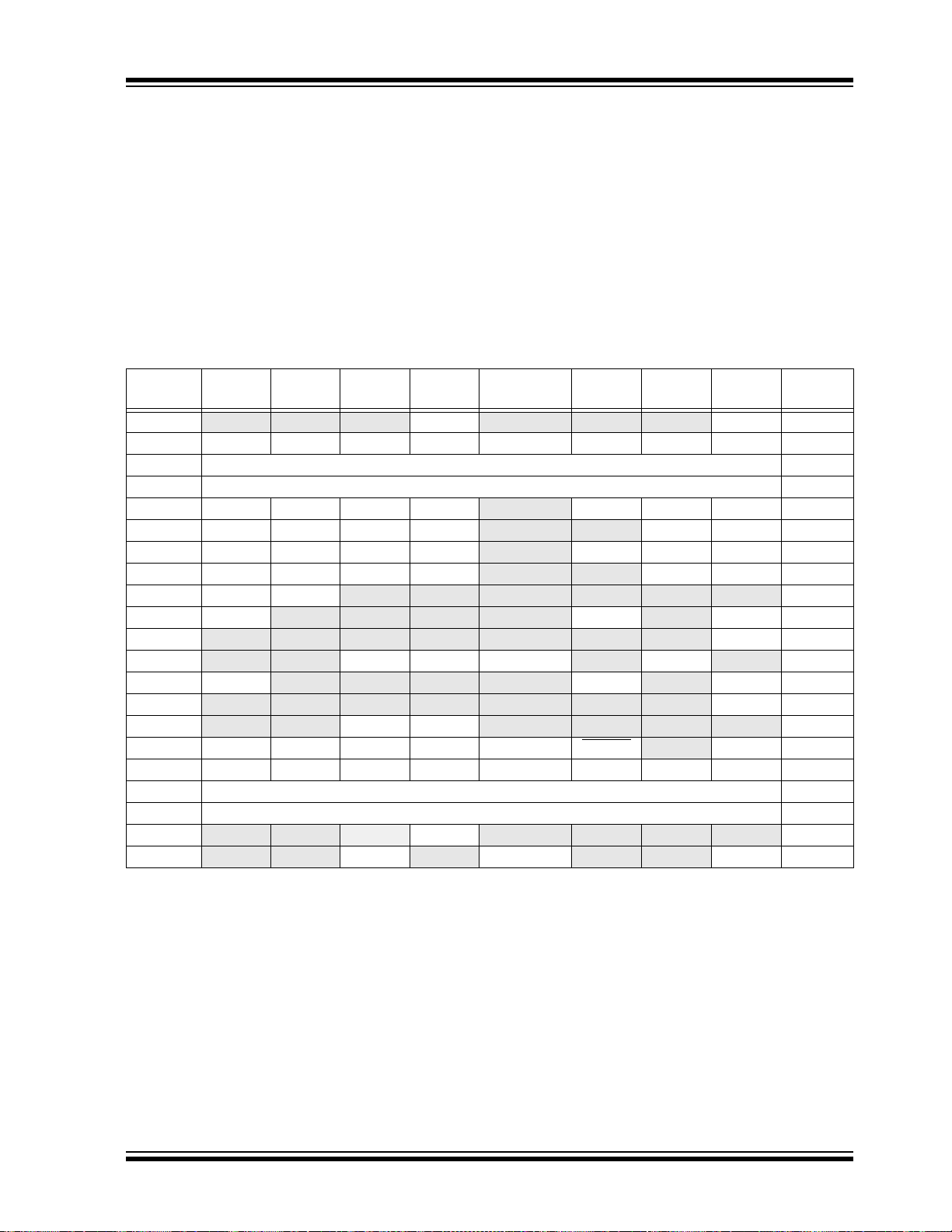

TABLE 24-4: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARE

Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Register

on Page

APFCON0

RXDTSEL SDO1SEL SS1SEL P2BSEL

(2)

CCP2SEL

(2)

P1DSEL P1CSEL CCP1SEL

119

CCPxCON PxM1

(1)

PxM0

(1)

DCxB1 DCxB0 CCPxM3 CCPxM2 CCPxM1 CCPxM0

226

CCPRxL Capture/Compare/PWM Register x Low Byte (LSB)

204*

CCPRxH Capture/Compare/PWM Register x High Byte (MSB)

204*

CM1CON0 C1ON C1OUT C1OE C1POL

— C1SP C1HYS C1SYNC

170

CM1CON1 C1INTP C1INTN C1PCH1 C1PCH0

— — C1NCH1 C1NCH0

171

CM2CON0 C2ON C2OUT C2OE C2POL

— C2SP C2HYS C2SYNC

170

CM2CON1 C2INTP C2INTN C2PCH1 C2PCH0

— — C2NCH1 C2NCH0

171

INTCON GIE PEIE

TMR0IE INTE IOCIE TMR0IF INTF IOCIF

86

PIE1 TMR1GIE

ADIE RCIE TXIE SSPIE CCP1IE TMR2IE TMR1IE

87

PIE2

OSFIE C2IE C1IE EEIE BCL1IE — — CCP2IE

(2)

88

PIE3

(2)

—

—

CCP4IE CCP3IE TMR6IE

—TMR4IE—

89

PIR1 TMR1GIF

ADIF RCIF TXIF SSPIF CCP1IF TMR2IF TMR1IF

91

PIR2

OSFIF C2IF C1IF EEIF BCLIF — —CCP2IF

(2)

92

PIR3

(2)

—

—

CCP4IF CCP3IF

TMR6IF — TMR4IF —

93

T1CON TMR1CS1 TMR1CS0 T1CKPS1 T1CKPS0 T1OSCEN T1SYNC

—TMR1ON

185

T1GCON TMR1GE T1GPOL T1GTM T1GSPM T1GGO/DONE T1GVAL T1GSS1 T1GSS0

186

TMR1L Holding Register for the Least Significant Byte of the 16-bit TMR1 Register

177*

TMR1H Holding Register for the Most Significant Byte of the 16-bit TMR1 Register

177*

TRISA

TRISA7 TRISA6 TRISA5 TRISA4 TRISA3 TRISA2 TRISA1 TRISA0

122

TRISB

TRISB7 TRISB6 TRISB5 TRISB4 TRISB3 TRISB2 TRISB1 TRISB0

127

Legend: — = Unimplemented locations, read as ‘0’. Shaded cells are not used by Compare mode.

* Page provides register information.

Note 1: Applies to ECCP modules only.

2: PIC16(L)F1827 only.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件