Datasheet 搜索 > NXP(恩智浦) > SGTL5000XNLA3/R2 数据手册 > SGTL5000XNLA3/R2 数据手册 1/68 页

¥ 0

SGTL5000XNLA3/R2 数据手册 - NXP(恩智浦)

制造商:

NXP(恩智浦)

封装:

HVQCCN

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P3P4Hot

典型应用电路图在P13P15P59P60

原理图在P2P12P20P23P59P60

封装尺寸在P61P62P63P64P65P66

型号编码规则在P1

封装信息在P61P62P63P64P65P66

功能描述在P3P12P13P14P15P16

技术参数、封装参数在P1P9

应用领域在P13P15P59P60

电气规格在P5P6P7P8P9P10P11P13

导航目录

SGTL5000XNLA3/R2数据手册

Page:

of 68 Go

若手册格式错乱,请下载阅览PDF原文件

Freescale Semiconductor, Inc. reserves the right to change the detail specifications,

as may be required, to permit improvements in the design of its products.

Document Number: SGTL5000

Rev. 6.0, 11/2013

Freescale Semiconductor

Technical Data

© Freescale Semiconductor, Inc., 2008-2013. All rights reserved.

Low Power Stereo Codec with

Headphone Amp

The SGTL5000 is a Low Power Stereo Codec with Headphone Amp

from Freescale, and is designed to provide a complete audio solution

for products needing LINEIN, MIC_IN, LINEOUT, headphone-out, and

digital I/O. Deriving it’s architecture from best in class, Freescale

integrated products that are currently on the market. The SGTL5000 is

able to achieve ultra low power with very high performance and

functionality, all in one of the smallest footprints available. Target

markets include media players, navigation devices, smart phones,

tablets, medical equipment, exercise equipment, consumer audio

equipment, etc. Features such as capless headphone design and an

internal PLL help lower overall system cost.

Features

Analog Inputs

• Stereo LINEIN - Support for external analog input

• Stereo LINEIN - Codec bypass for low power

• MIC bias provided

• Programmable MIC gain

• ADC - 85 dB SNR (-60 dB input) and -73 dB THD+N

(VDDA

= 1.8 V)

Analog Outputs

• HP Output - Capless design

• HP Output - 62.5 mW max, 1.02 kHz sine into 16 load at 3.3 V

• HP Output - 100 dB SNR (-60 dB input) and -80 dB THD+N

(V

DDA

= 1.8 V, 16 load, DAC to headphone)

• LINEOUT - 100 dB SNR (-60 dB input) and -85 dB THD+N

(V

DDIO

= 3.3 V)

Digital I/O

•I

2

S port to allow routing to Application Processor

Integrated Digital Processing

• Freescale surround, Freescale bass, tone control/ parametric

equalizer/graphic equalizer clocking/control

• PLL allows input of an 8.0 MHz to 27 MHz system clock - standard

audio clocks are derived from PLL

Power Supplies

• Designed to operate from 1.62 to 3.6 volts

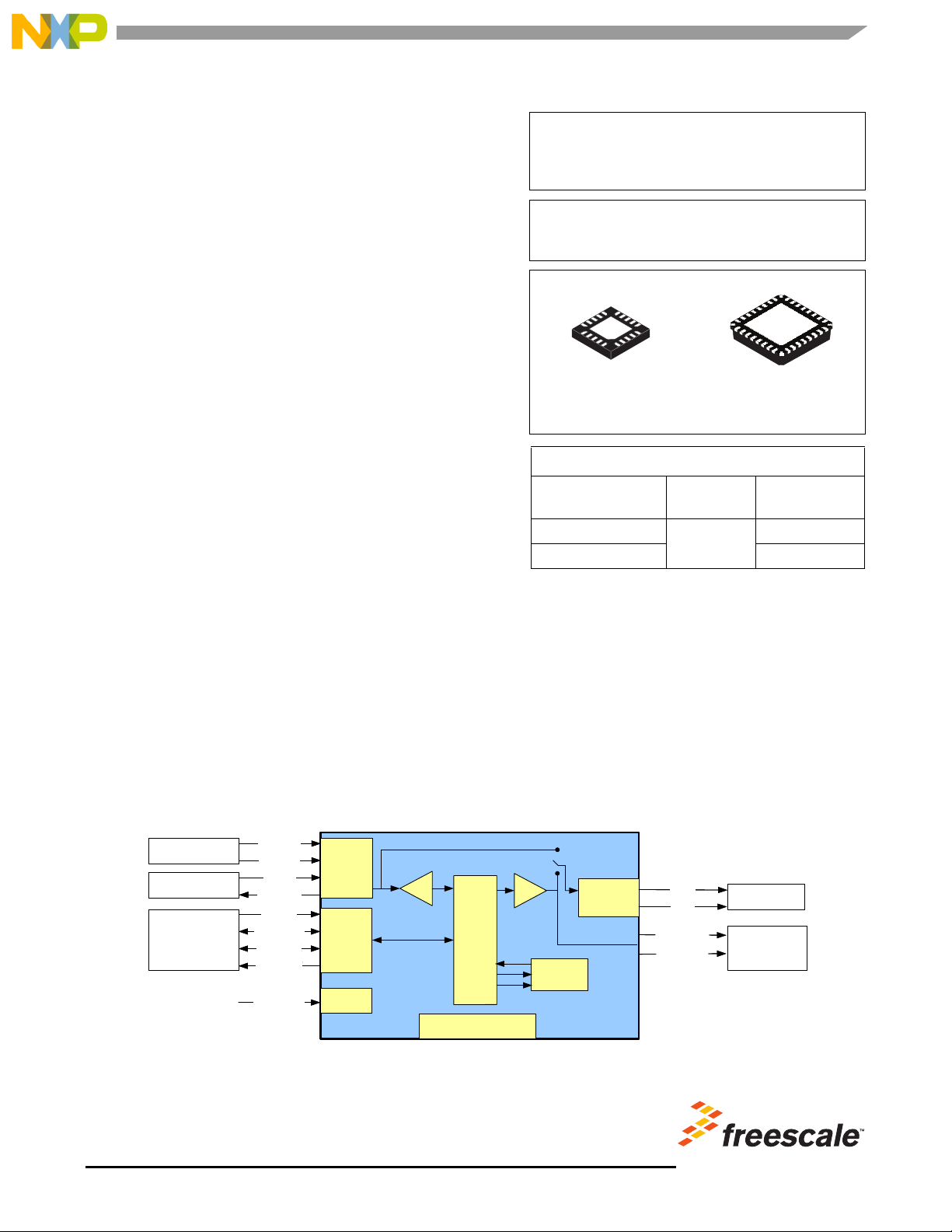

Figure 1. SGTL5000 Simplified Application Diagram

AUDIO CODEC

SGTL5000

ORDERING INFORMATION

Device

Temperature

Range (T

A

)

Package

SGTL5000XNLA3/R2

-40 to 85 °C

20 QFN

SGTL5000XNAA3/R2

32 QFN

PB-FREE

98ARE10742D

20-PIN QFN

PB-FREE

98ARE10739D

32-PIN QFN

I2S

Interface

Headphone /

Line Out

w/ volume

Audio

Switch

ADC

DAC

I2S_DOUT

I2S_DIN

I2S_SCLK

I2S_LRCLK

L

I

N

E

O

U

T

_

R

L

I

N

E

O

U

T

_

L

H

P

_

R

HP_L

I2C/SPI Control

SYS_MCLK

PLL

Application

Processor

Headphone

Speaker

Amp/Docking

Station/FMTX

Audio

Processing

Analog In

(Stereo

Line In,

MIC)

LINEIN_R

LINEIN_L

MIC_IN

MIC_BIAS

MP3/FM Input

MIC IN/Speech

Recognition

I2S

Interface

Headphone /

Line Out

w/ volume

Audio

Switch

ADC

DAC

I2S_DOUT

I2S_DIN

I2S_SCLK

I2S_LRCLK

L

I

N

E

O

U

T

_

R

L

I

N

E

O

U

T

_

L

H

P

_

R

HP_L

I2C/SPI Control

SYS_MCLK

PLL

Application

Processor

Headphone

Speaker

Amp/Docking

Station/FMTX

Audio

Processing

Analog In

(Stereo

Line In,

MIC)

LINEIN_R

LINEIN_L

MIC_IN

MIC_BIAS

MP3/FM Input

MIC IN/Speech

Recognition

Note: SPI is not supported in the 3.0 mm x 3.0 mm 20-pin QFN package

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件