Datasheet 搜索 > 接口芯片 > TI(德州仪器) > SN75LBC176AP 数据手册 > SN75LBC176AP 数据手册 5/20 页

器件3D模型

器件3D模型¥ 32.281

SN75LBC176AP 数据手册 - TI(德州仪器)

制造商:

TI(德州仪器)

分类:

接口芯片

封装:

PDIP-8

描述:

差分总线收发器 DIFFERENTIAL BUS TRANSCEIVERS

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

封装尺寸在P13P15P16

标记信息在P13P14

封装信息在P13P14P15P16

应用领域在P1P14P20

导航目录

SN75LBC176AP数据手册

Page:

of 20 Go

若手册格式错乱,请下载阅览PDF原文件

SLLS376D− MAY 2000 − REVISED JULY 2008

5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

POST OFFICE BOX 1443

• HOUSTON, TEXAS 77251−1443

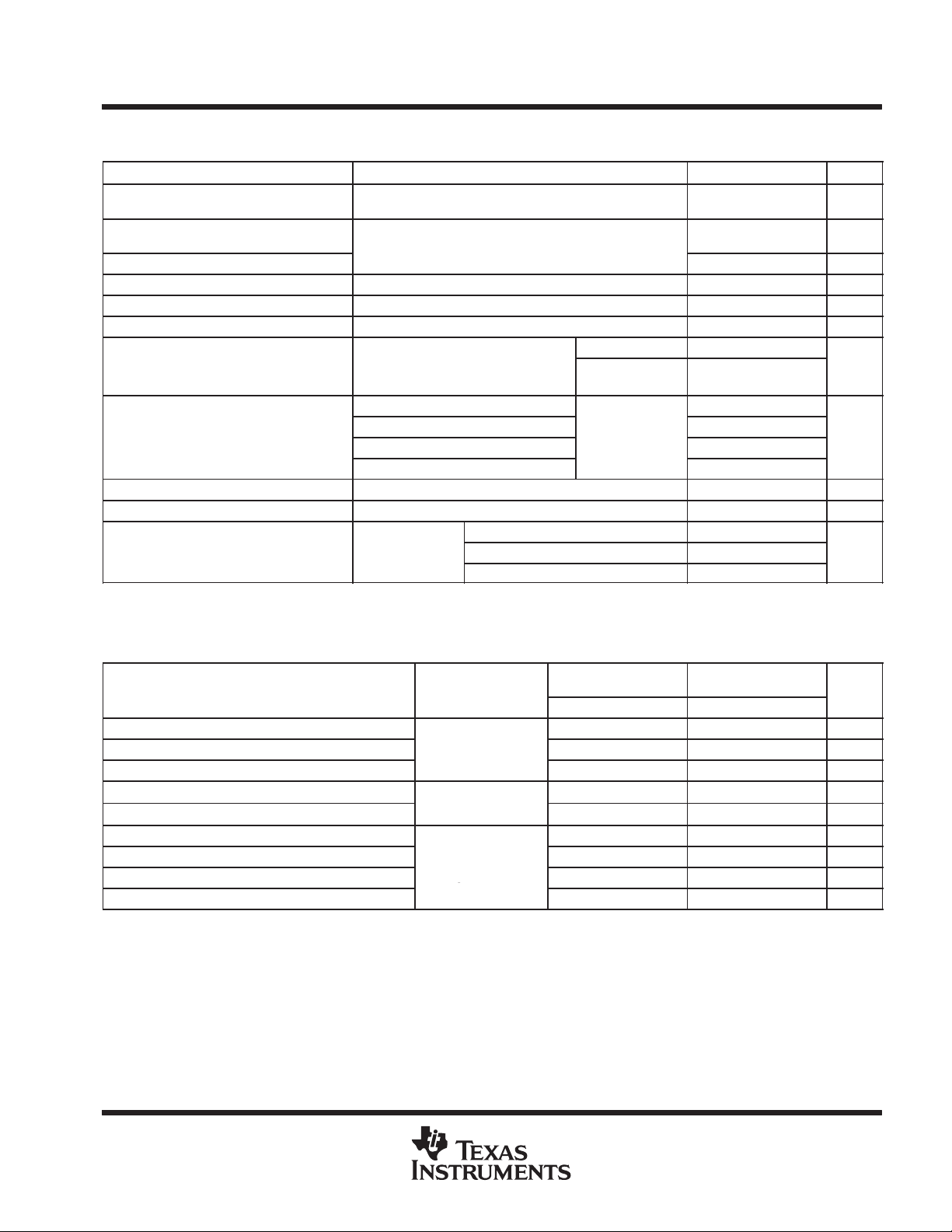

receiver electrical characteristics over recommended operating conditions (unless otherwise

noted)

PARAMETER TEST CONDITIONS MIN

TYP

†

MAX UNIT

V

IT+

Positive-going input threshold

voltage

I

O

= −8 mA 0.2 V

V

IT−

Negative-going input threshold

voltage

I

O

= 8 mA

−0.2 V

V

hys

Hysteresis voltage (V

IT+

− V

IT−

)

I

O

= 8 mA

50 mV

V

IK

Enable-input clamp voltage I

I

= −18 mA −1.5 −0.8 V

V

OH

High-level output voltage V

ID

= 200 mV, I

OH

= −8 mA, See Figure 6 4 4.9 V

V

OL

Low-level output voltage V

ID

= −200 mV, I

OL

= 8 mA, See Figure 6 0.1 0.8 V

High-impedance-state output

SN65LBC176AQ −10 10

I

OZ

High-impedance-state output

current

V

O

= 0 to V

CC

SN65LBC176A,

SN75LBC176A

−1 1

µA

V

IH

= 12 V, V

CC

= 5 V 0.4 1

I

I

Bus input current

V

IH

= 12 V, V

CC

= 0

Other input at 0 V

0.5 1

mA

I

I

Bus input current

V

IH

= −7 V,

V

CC

= 5 V

Other input at 0 V

−0.8 −0.4

mA

V

IH

= −7 V, V

CC

= 0 −0.8 −0.3

I

IH

High-level enable-input current V

IH

= 2 V −100 µA

I

IL

Low-level enable-input current V

IL

= 0.8 V −100 µA

V

I

= 0 or V

CC

,

Receiver enabled and driver disabled 4 7

I

CC

Supply current

V

I

= 0 or V

CC

,

No load

Receiver disabled and driver disabled 0.4 0.7

mA

I

CC

Supply current

No load

Receiver enabled and driver enabled 8.5 15

mA

†

All typical values are at V

CC

= 5 V, T

A

= 25°C.

receiver switching characteristics over recommended operating conditions (unless otherwise

noted)

PARAMETER

TEST CONDITIONS

SN65LBC176AQ

SN65LBC176A

SN75LBC176A

UNIT

PARAMETER

TEST CONDITIONS

MIN TYP

†

MAX MIN TYP

†

MAX

UNIT

t

PLH

Propagation delay time, output↑

V

ID

= −1.5 V to 1.5 V,

7 30 7 13 20 ns

t

PHL

Propagation delay time, output↓

V

ID

= −1.5 V to 1.5 V

,

See Figure 7

7 30 7 13 20 ns

t

sk(p)

Pulse skew (| t

PHL

− t

PLH

|)

See Figure 7

6 0.5 1.5 ns

t

r

Rise time, output

See Figure 7

5 2.1 3.3 ns

t

f

Fall time, output

See Figure 7

5 2.1 3.3 ns

t

PZH

Output enable time to high level 50 30 45 ns

t

PZL

Output enable time to low level

C

L

= 10 pF,

50 30 45 ns

t

PHZ

Output disable time from high level

C

L

= 10 pF,

See Figure 8

60 20 40 ns

t

PLZ

Output disable time from low level

See Figure 8

40 20 40 ns

†

All typical values are at V

CC

= 5 V, T

A

= 25°C.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件