Datasheet 搜索 > ST Microelectronics(意法半导体) > STM32F417IGH6TR 数据手册 > STM32F417IGH6TR 数据手册 140/206 页

器件3D模型

器件3D模型¥ 323.808

STM32F417IGH6TR 数据手册 - ST Microelectronics(意法半导体)

制造商:

ST Microelectronics(意法半导体)

封装:

UFBGA

描述:

ARM微控制器 - MCU High-performance foundation line, ARM Cortex-M4 core with DSP and FPU, 1 Mbyte Flash, 168 MHz CPU, ART Accelerator, Ethernet, FSMC, HW crypto

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P44P45P46P47P48P49P50P51P52P53P54P55Hot

典型应用电路图在P106P107P140

封装尺寸在P168P169P170P171P172P173P174P175P176P177P178P179

型号编码规则在P189

技术参数、封装参数在P81P116

电气规格在P79P80P81P82P83P84P85P86P87P88P89P90

导航目录

STM32F417IGH6TR数据手册

Page:

of 206 Go

若手册格式错乱,请下载阅览PDF原文件

Electrical characteristics STM32F415xx, STM32F417xx

140/206 DocID022063 Rev 8

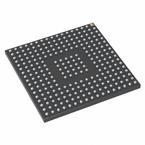

Figure 49. ADC accuracy characteristics

1. See also Table 68.

2. Example of an actual transfer curve.

3. Ideal transfer curve.

4. End point correlation line.

5. E

T

= Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves.

EO = Offset Error: deviation between the first actual transition and the first ideal one.

EG = Gain Error: deviation between the last ideal transition and the last actual one.

ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one.

EL = Integral Linearity Error: maximum deviation between any actual transition and the end point

correlation line.

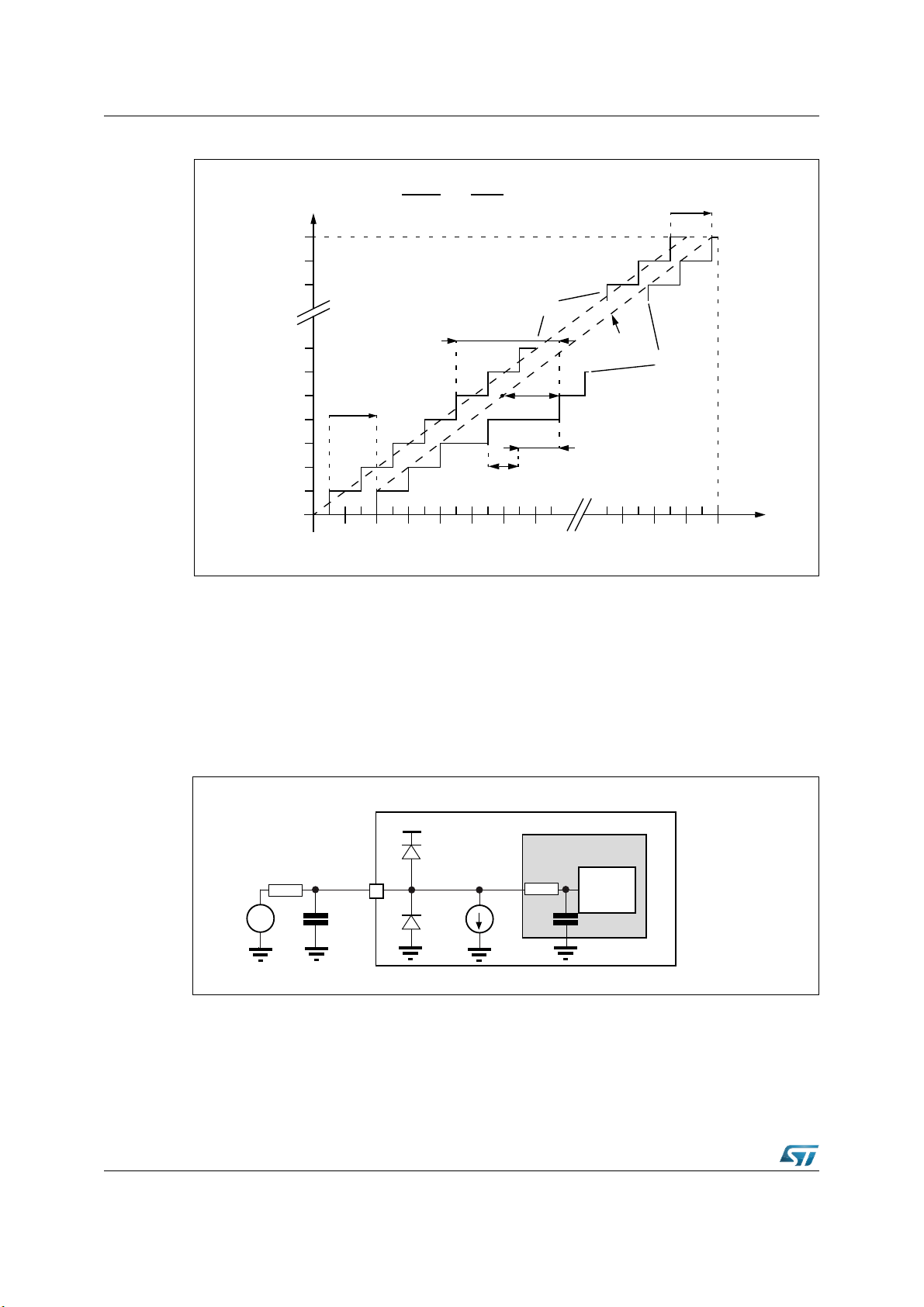

Figure 50. Typical connection diagram using the ADC

1. Refer to Table 67 for the values of R

AIN

, R

ADC

and C

ADC

.

2. C

parasitic

represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the

pad capacitance (roughly 5

pF). A high C

parasitic

value downgrades conversion accuracy. To remedy this,

f

ADC

should be reduced.

AIC

%

/

%

'

, 3"

)$%!,

%

4

%

$

%

,

6

$$!

6

33!

6

2%&

ORDEPENDINGONPACKAGE=

6

$$!

;,3"

)$%!,

DL

670)

9

''

$,1[

,

/

$

9

9

7

5

$,1

&

SDUDVLWLF

9

$,1

9

9

7

5

$'&

&

$'&

ELW

FRQYHUWHU

6DPSOHDQGKROG$'&

FRQYHUWHU

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件