Datasheet 搜索 > SOC(赛元微) > M2S090-1FG484I 数据手册 > M2S090-1FG484I 产品描述及参数 1/58 页

器件3D模型

器件3D模型¥ 1303.862

M2S090-1FG484I 产品描述及参数 - SOC(赛元微)

制造商:

SOC(赛元微)

封装:

BGA-484

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P1P2P3P4P5P6P7P8P9P10P11P12Hot

封装尺寸在P44P45P46P47P48P49P50P51P54P55

封装信息在P44P45P46P47P48P49P50P51

应用领域在P57

导航目录

M2S090-1FG484I数据手册

Page:

of 58 Go

若手册格式错乱,请下载阅览PDF原文件

December 2015 1

© 2015 Microsemi Corporation

SmartFusion2 Pin Descriptions

User I/Os

SmartFusion

®

2 system-on-chip (SoC) field programmable gate array (FPGA) devices feature a flexible

I/O structure that supports a range of mixed voltages (1.2 V, 1.5 V, 1.8 V, 2.5 V, and 3.3 V) through bank

selection. The MSIO, MSIOD, and DDRIO can be configured as differential I/Os or two single-ended

I/Os. These I/Os use one I/O slot to implement single-ended standards and two I/O slots for differential

standards. The DDRIO is shared between fabric logic and MDDR/FDDR whereas MSIO/MSIOD is

shared between MSS peripherals and fabric logic. When an MDDR/FDDR controller or MSS peripheral is

not used, the respective I/Os are available to fabric logic.

For functional block diagrams of MSIO, MSIOD, and DDRIO, refer to the UG0445: IGLOO2 FPGA and

SmartFusion2 SoC FPGA Fabric User Guide.

For supported I/O standards, refer to the “Supported Voltage Standards” table in the UG0445: IGLOO2

FPGA and SmartFusion2 SoC FPGA Fabric User Guide.

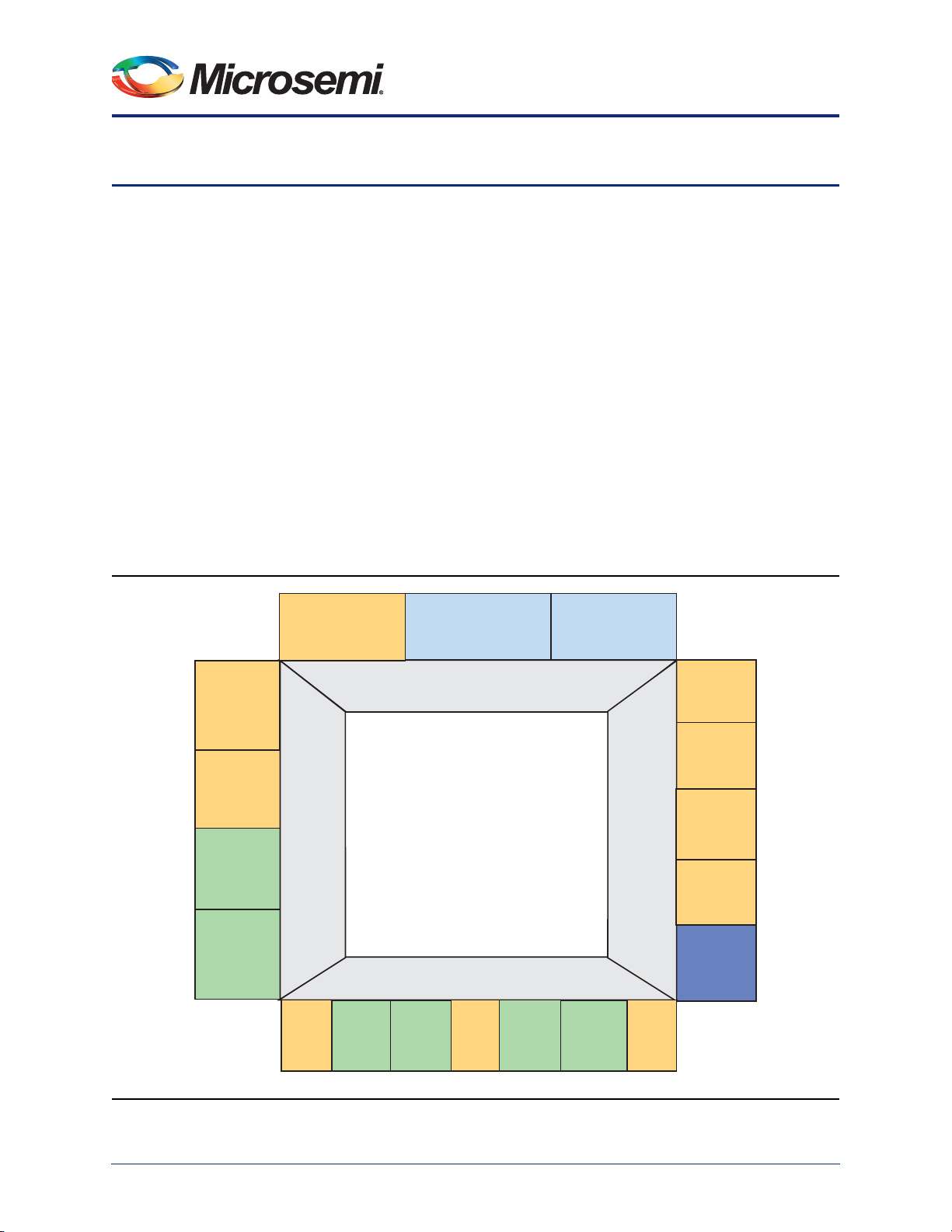

Bank Location Diagrams

I/Os are grouped on the basis of I/O voltage standard. The grouped I/Os of each voltage standard form

an I/O bank. Each I/O bank has dedicated I/O supply and ground voltages. Because of these dedicated

supplies, only I/Os with compatible standards can be assigned to the same I/O voltage bank.

Note: For M2S150-FC1152 device, SERDES blocks are not available in bank 9, 10, 12, and 13.

Figure 1 • SmartFusion2 M2S150TS/M2S150T/M2S150-FC1152 I/O Bank Locations

West

East

Bank 1

DDRIO / FDDR

(44 pairs)

Bank 3

MSIO

(21 pairs)

Bank 15

MSIOD

(18 pairs)

Bank 16

MSIOD

(27 pairs)

Bank 4

MSIO

(22 pairs)

Bank 17

MSIO

(20 pairs)

North

South

SmartFusion2

SoC FPGA

M2S150TS/M2S150T/M2S150

FC1152

Bank 5

MSIO

(21 pairs)

Bank 18

MSIO

(21 pairs)

Bank 7

JTAG

Bank 6

MSIO

(15 pairs)

Bank 14

MSIO

(7 pairs)

Bank 13

MSIOD /

SERDES0

(2 pairs)

Bank 12

MSIOD /

SERDES1

(2 pairs)

Bank 11

MSIO

(4 pairs)

Bank 10

MSIOD /

SERDES2

(2 pairs)

Bank 9

MSIOD /

SERDES3

(2 pairs)

Bank 8

MSIO

(9 pairs)

Bank 2

DDRIO / MDDR

(44 pairs)

Bank 0

MSIO

(6 pairs)

Revision 10

DS0115

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件