Datasheet 搜索 > CPLD芯片 > Altera(阿尔特拉) > EPM7032SLC44-10 数据手册 > EPM7032SLC44-10 用户编程技术手册 3/66 页

器件3D模型

器件3D模型¥ 7.181

EPM7032SLC44-10 用户编程技术手册 - Altera(阿尔特拉)

制造商:

Altera(阿尔特拉)

分类:

CPLD芯片

封装:

PLCC-44

描述:

EPM7032SLC44-10 管装

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

EPM7032SLC44-10数据手册

Page:

of 66 Go

若手册格式错乱,请下载阅览PDF原文件

Altera Corporation 3

MAX 7000 Programmable Logic Device Family Data Sheet

■ Additional design entry and simulation support provided by EDIF

2 0 0 and 3 0 0 netlist files, library of parameterized modules (LPM),

Verilog HDL, VHDL, and other interfaces to popular EDA tools from

manufacturers such as Cadence, Exemplar Logic, Mentor Graphics,

OrCAD, Synopsys, and VeriBest

■ Programming support

– Altera’s Master Programming Unit (MPU) and programming

hardware from third-party manufacturers program all

MAX 7000 devices

–The BitBlaster

TM

serial download cable, ByteBlasterMV

TM

parallel port download cable, and MasterBlaster

TM

serial/universal serial bus (USB) download cable program MAX

7000S devices

General

Description

The MAX 7000 family of high-density, high-performance PLDs is based

on Altera’s second-generation MAX architecture. Fabricated with

advanced CMOS technology, the EEPROM-based MAX 7000 family

provides 600 to 5,000 usable gates, ISP, pin-to-pin delays as fast as 5 ns,

and counter speeds of up to 175.4 MHz. MAX 7000S devices in the -5, -6,

-7, and -10 speed grades as well as MAX 7000 and MAX 7000E devices in

-5, -6, -7, -10P, and -12P speed grades comply with the PCI Special Interest

Group (PCI SIG) PCI Local Bus Specification, Revision 2.2. See Table 3

for available speed grades.

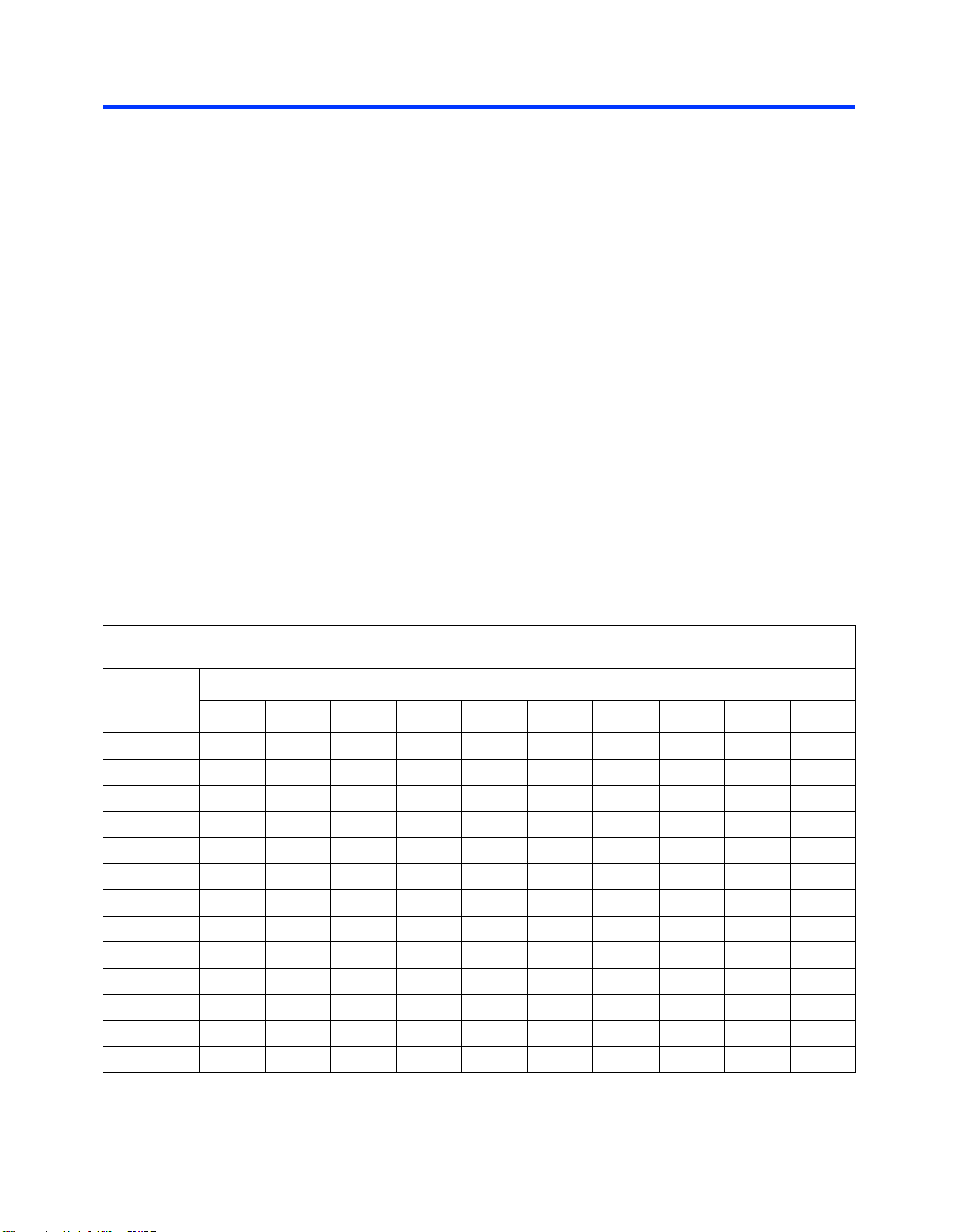

Table 3. MAX 7000 Speed Grades

Device Speed Grade

-5 -6 -7 -10P -10 -12P -12 -15 -15T -20

EPM7032

vv v vvv

EPM7032S

v v v v

EPM7064

vvvvv

EPM7064S

v v v v

EPM7096

vvvv

EPM7128E

vvv vv v

EPM7128S

v v v v

EPM7160E

vv vv v

EPM7160S

vv v v

EPM7192E

vvv v

EPM7192S

vv v

EPM7256E

vvv v

EPM7256S

vv v

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件