Datasheet 搜索 > EEPROM芯片 > Xilinx(赛灵思) > XCF01SVOG20C 数据手册 > XCF01SVOG20C 用户编程技术手册 1/48 页

器件3D模型

器件3D模型¥ 103.118

XCF01SVOG20C 用户编程技术手册 - Xilinx(赛灵思)

制造商:

Xilinx(赛灵思)

分类:

EEPROM芯片

封装:

TSSOP-20

描述:

XILINX XCF01SVOG20C 芯片, 存储器, PROM, 闪存平台, 1Mb, 20TSSOP

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P38P39P40P41P42Hot

原理图在P2P48

型号编码规则在P44

标记信息在P44P45P48

封装信息在P27

技术参数、封装参数在P27P38P47P48

应用领域在P48

电气规格在P27P30P47

导航目录

XCF01SVOG20C数据手册

Page:

of 48 Go

若手册格式错乱,请下载阅览PDF原文件

DS123 (v2.15) July 07, 2008 www.xilinx.com

Product Specification 1

© 2003–2008 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, Virtex, Spartan, ISE and other designated brands included herein are trademarks of Xilinx in the United

States and other countries. All other trademarks are the property of their respective owners.

Features

• In-System Programmable PROMs for Configuration of

Xilinx

®

FPGAs

• Low-Power Advanced CMOS NOR Flash Process

• Endurance of 20,000 Program/Erase Cycles

• Operation over Full Industrial Temperature Range

(–40°C to +85°C)

• IEEE Standard 1149.1/1532 Boundary-Scan (JTAG)

Support for Programming, Prototyping, and Testing

• JTAG Command Initiation of Standard FPGA

Configuration

• Cascadable for Storing Longer or Multiple Bitstreams

•

Dedicated Boundary-Scan (JTAG) I/O Power Supply (V

CCJ

)

• I/O Pins Compatible with Voltage Levels Ranging From

1.5V to 3.3V

• Design Support Using the Xilinx Alliance ISE

®

and

Foundation™ ISE Series Software Packages

• XCF01S/XCF02S/XCF04S

♦ 3.3V Supply Voltage

♦ Serial FPGA Configuration Interface (up to 33 MHz)

♦ Available in Small-Footprint VO20 and VOG20

Packages

• XCF08P/XCF16P/XCF32P

♦ 1.8V Supply Voltage

♦ Serial or Parallel FPGA Configuration Interface

(upto33MHz)

♦ Available in Small-Footprint VO48, VOG48, FS48,

and FSG48 Packages

♦ Design Revision Technology Enables Storing and

Accessing Multiple Design Revisions for

Configuration

♦ Built-In Data Decompressor Compatible with Xilinx

Advanced Compression Technology

Description

Xilinx introduces the Platform Flash series of in-system

programmable configuration PROMs. Available in 1 to 32

Megabit (Mbit) densities, these PROMs provide an easy-to-

use, cost-effective, and reprogrammable method for storing

large Xilinx FPGA configuration bitstreams. The Platform

Flash PROM series includes both the 3.3V XCFxxS PROM

and the 1.8V XCFxxP PROM. The XCFxxS version includes

4-Mbit, 2-Mbit, and 1-Mbit PROMs that support Master

Serial and Slave Serial FPGA configuration modes

(Figure 1, page 2). The XCFxxP version includes 32-Mbit,

16-Mbit, and 8-Mbit PROMs that support Master Serial,

Slave Serial, Master SelectMAP, and Slave SelectMAP

FPGA configuration modes (Figure 2, page 2). A summary

of the Platform Flash PROM family members and supported

features is shown in Table 1 .

48

Platform Flash In-System Programmable

Configuration PROMs

DS123 (v2.15) July 07, 2008

0

Product Specification

R

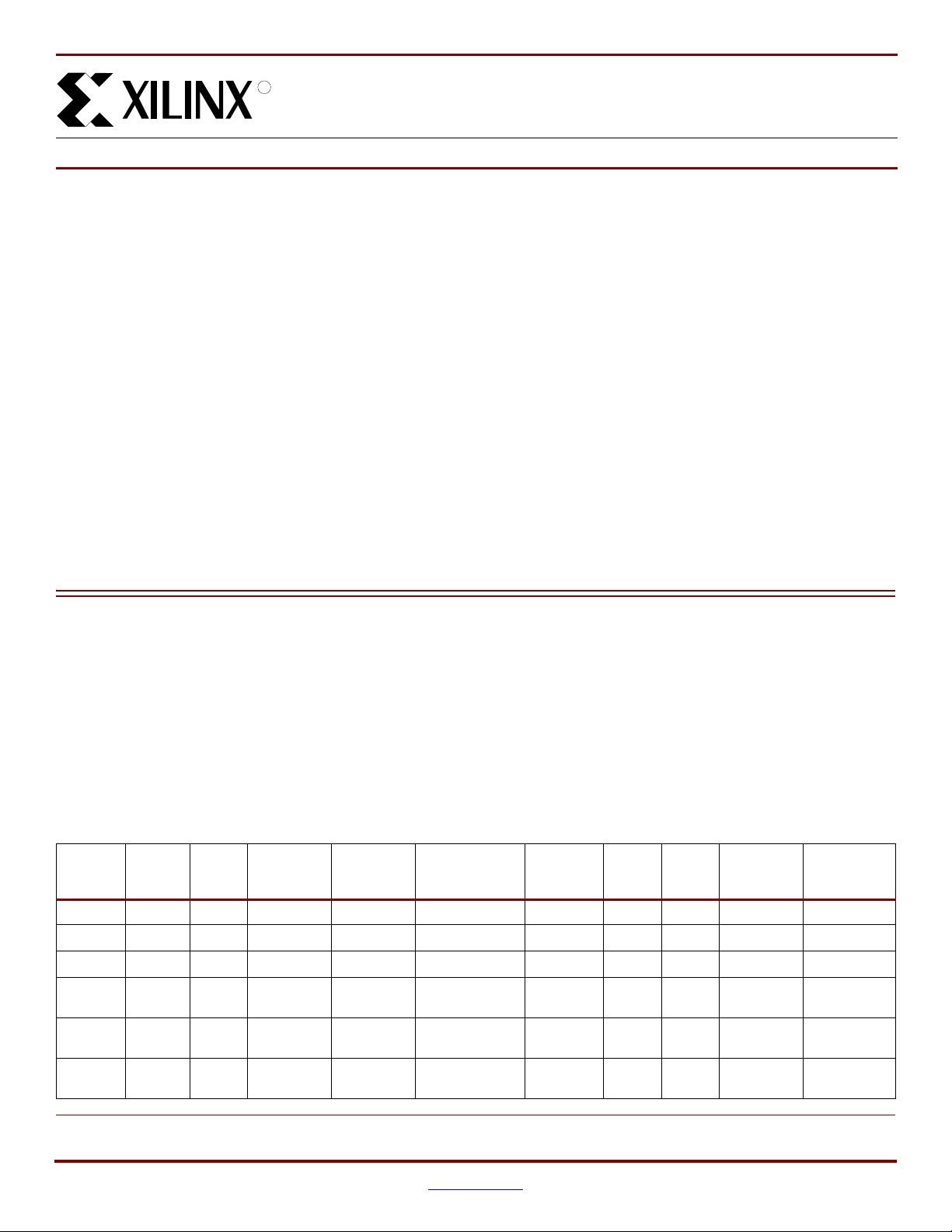

Table 1 : Platform Flash PROM Features

Device Density V

CCINT

V

CCO

Range V

CCJ

Range Packages

Program

In-system

via JTAG

Serial

Config.

Parallel

Config.

Design

Revisioning

Compression

XCF01S 1 Mbit 3.3V 1.8V – 3.3V 2.5V – 3.3V VO20/VOG20 33

XCF02S 2 Mbit 3.3V 1.8V – 3.3V 2.5V – 3.3V VO20/VOG20

33

XCF04S 4 Mbit 3.3V 1.8V – 3.3V 2.5V – 3.3V VO20/VOG20

33

XCF08P 8 Mbit 1.8V 1.5V – 3.3V 2.5V – 3.3V

VO48/VOG48

FS48/FSG48

333 3 3

XCF16P 16 Mbit 1.8V 1.5V – 3.3V 2.5V – 3.3V

VO48/VOG48

FS48/FSG48

333 3 3

XCF32P 32 Mbit 1.8V 1.5V – 3.3V 2.5V – 3.3V

VO48/VOG48

FS48/FSG48

333 3 3

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件