Datasheet 搜索 > Intel(英特尔) > 5AGXFB3H4F35I3 数据手册 > 5AGXFB3H4F35I3 数据手册 29/183 页

¥ 15691.415

5AGXFB3H4F35I3 数据手册 - Intel(英特尔)

制造商:

Intel(英特尔)

封装:

BGA

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P10P11P19P27P31Hot

技术参数、封装参数在P4P5P14P15P16P18P19P21P22P25P26P27

电气规格在P4P104

导航目录

5AGXFB3H4F35I3数据手册

Page:

of 183 Go

若手册格式错乱,请下载阅览PDF原文件

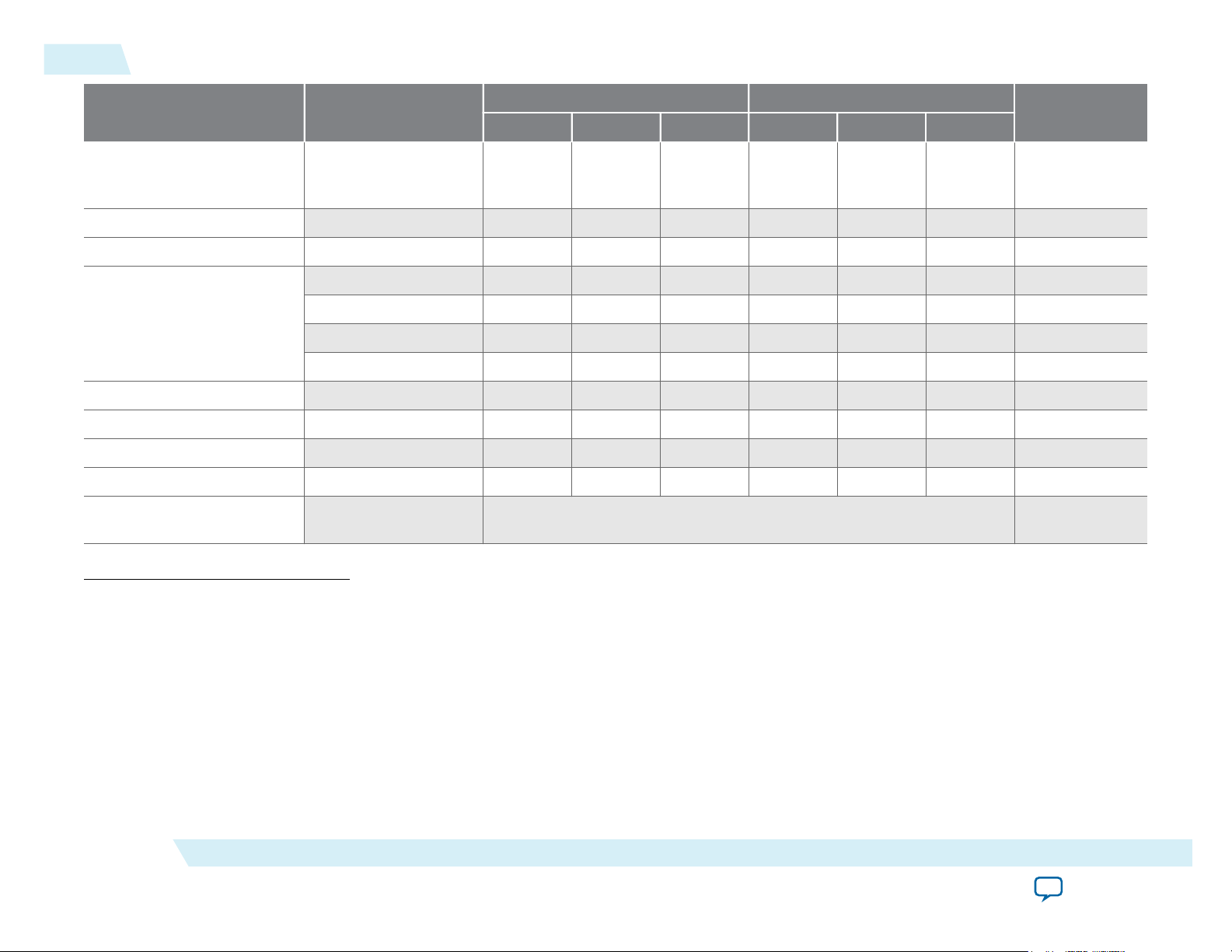

Symbol/Description Condition

Transceiver Speed Grade 4 Transceiver Speed Grade 6

Unit

Min Typ Max Min Typ Max

Minimum differential eye

opening at the receiver

serial input pins

(30)

— 100 — — 100 — — mV

V

ICM

(AC coupled) — — 650

(31)

/800 — — 650

(31)

/800 — mV

V

ICM

(DC coupled) ≤ 3.2Gbps

(32)

670 700 730 670 700 730 mV

Differential on-chip

termination resistors

85-Ω setting — 85 — — 85 — Ω

100-Ω setting — 100 — — 100 — Ω

120-Ω setting — 120 — — 120 — Ω

150-Ω setting — 150 — — 150 — Ω

t

LTR

(33)

— — — 10 — — 10 µs

t

LTD

(34)

— 4 — — 4 — — µs

t

LTD_manual

(35)

— 4 — — 4 — — µs

t

LTR_LTD_manual

(36)

— 15 — — 15 — — µs

Programmable ppm

detector

(37)

— ±62.5, 100, 125, 200, 250, 300, 500, and 1000 ppm

(30)

The differential eye opening specification at the receiver input pins assumes that you have disabled the Receiver Equalization feature. If you enable

the Receiver Equalization feature, the receiver circuitry can tolerate a lower minimum eye opening, depending on the equalization level.

(31)

The AC coupled V

ICM

is 650 mV for PCIe mode only.

(32)

For standard protocol compliance, use AC coupling.

(33)

t

LTR

is the time required for the receive CDR to lock to the input reference clock frequency after coming out of reset.

(34)

t

LTD

is time required for the receiver CDR to start recovering valid data after the rx_is_lockedtodata signal goes high.

(35)

t

LTD_manual

is the time required for the receiver CDR to start recovering valid data after the rx_is_lockedtodata signal goes high when the CDR is

functioning in the manual mode.

(36)

t

LTR_LTD_manual

is the time the receiver CDR must be kept in lock to reference (LTR) mode after the rx_is_lockedtoref signal goes high when the

CDR is functioning in the manual mode.

(37)

The rate match FIFO supports only up to ±300 parts per million (ppm).

1-26

Transceiver Specifications for Arria V GX and SX Devices

AV-51002

2016.06.10

Altera Corporation

Arria V GX, GT, SX, and ST Device Datasheet

Send Feedback

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件