Datasheet 搜索 > FPGA芯片 > Altera(阿尔特拉) > 5AGXFB3H4F35I3G 数据手册 > 5AGXFB3H4F35I3G 数据手册 20/183 页

器件3D模型

器件3D模型¥ 18582.542

5AGXFB3H4F35I3G 数据手册 - Altera(阿尔特拉)

制造商:

Altera(阿尔特拉)

分类:

FPGA芯片

封装:

BBGA-1152

描述:

FPGA - 现场可编程门阵列

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P10P11P19P27P31Hot

技术参数、封装参数在P4P5P14P15P16P18P19P21P22P25P26P27

电气规格在P4P104

导航目录

5AGXFB3H4F35I3G数据手册

Page:

of 183 Go

若手册格式错乱,请下载阅览PDF原文件

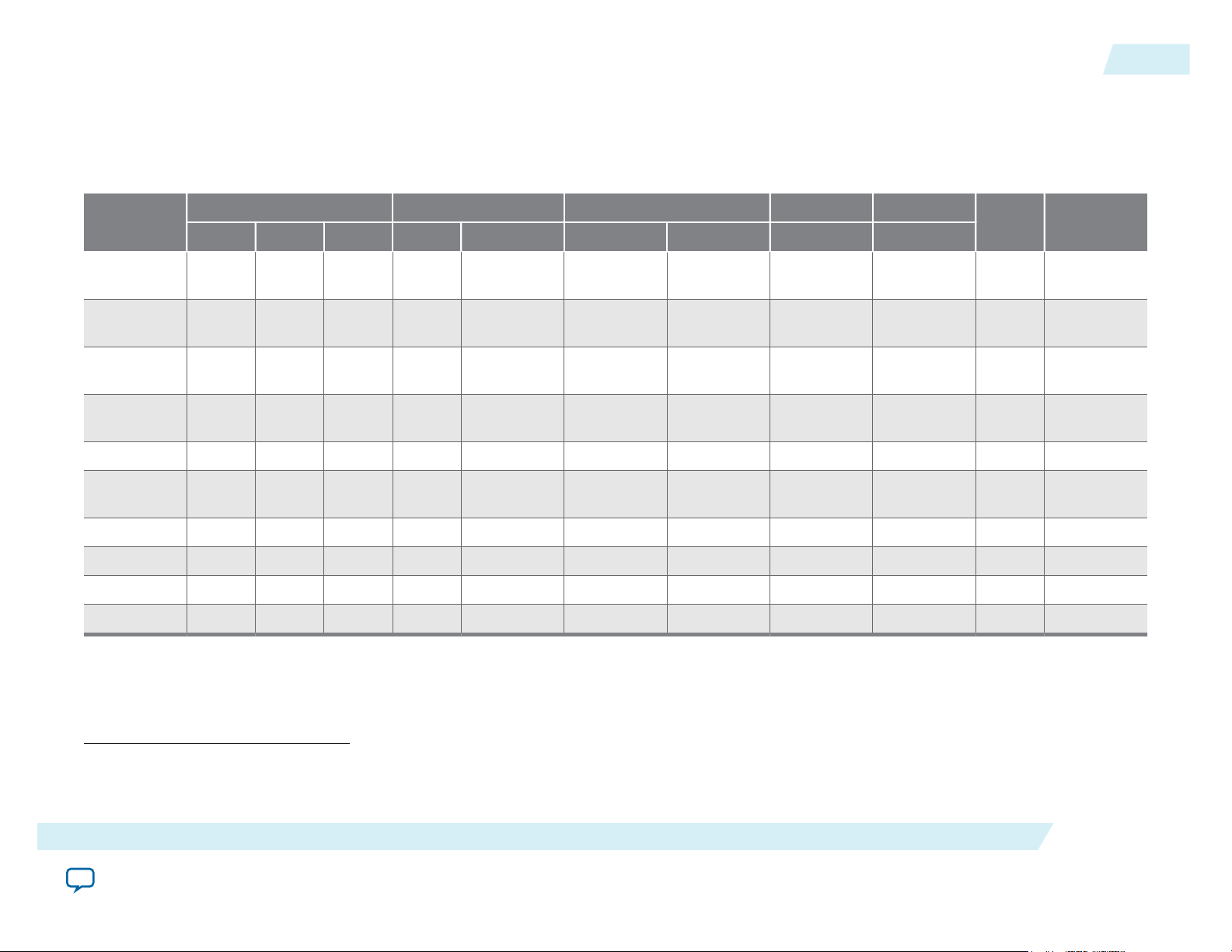

You must perform timing closure analysis to determine the maximum achievable frequency for general purpose I/O standards.

Single-Ended I/O Standards

Table 1-14: Single-Ended I/O Standards for Arria V Devices

I/O Standard

V

CCIO

(V) V

IL

(V) V

IH

(V) V

OL

(V) V

OH

(V)

I

OL

(13)

(mA)

I

OH

(13)

(mA)

Min Typ Max Min Max Min Max Max Min

3.3-V

LVTTL

3.135 3.3 3.465 –0.3 0.8 1.7 3.6 0.45 2.4 4 –4

3.3-V

LVCMOS

3.135 3.3 3.465 –0.3 0.8 1.7 3.6 0.2 V

CCIO

– 0.2 2 –2

3.0-V

LVTTL

2.85 3 3.15 –0.3 0.8 1.7 3.6 0.4 2.4 2 –2

3.0-V

LVCMOS

2.85 3 3.15 –0.3 0.8 1.7 3.6 0.2 V

CCIO

– 0.2 0.1 –0.1

3.0-V PCI 2.85 3 3.15 — 0.3 × V

CCIO

0.5 × V

CCIO

V

CCIO

+ 0.3 0.1 × V

CCIO

0.9 × V

CCIO

1.5 –0.5

3.0-V

PCI-X

2.85 3 3.15 — 0.35 × V

CCIO

0.5 × V

CCIO

V

CCIO

+ 0.3 0.1 × V

CCIO

0.9 × V

CCIO

1.5 –0.5

2.5 V 2.375 2.5 2.625 –0.3 0.7 1.7 3.6 0.4 2 1 –1

1.8 V 1.71 1.8 1.89 –0.3 0.35 × V

CCIO

0.65 × V

CCIO

V

CCIO

+ 0.3 0.45 V

CCIO

– 0.45 2 –2

1.5 V 1.425 1.5 1.575 –0.3 0.35 × V

CCIO

0.65 × V

CCIO

V

CCIO

+ 0.3 0.25 × V

CCIO

0.75 × V

CCIO

2 –2

1.2 V 1.14 1.2 1.26 –0.3 0.35 × V

CCIO

0.65 × V

CCIO

V

CCIO

+ 0.3 0.25 × V

CCIO

0.75 × V

CCIO

2 –2

(13)

To meet the I

OL

and I

OH

specifications, you must set the current strength settings accordingly. For example, to meet the 3.3-V LVTTL specification

(4 mA), you should set the current strength settings to 4 mA. Setting at lower current strength may not meet the I

OL

and I

OH

specifications in the

datasheet.

AV-51002

2016.06.10

Single-Ended I/O Standards

1-17

Arria V GX, GT, SX, and ST Device Datasheet

Altera Corporation

Send Feedback

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件