Datasheet 搜索 > DA转换器 > ADI(亚德诺) > AD5331BRU-REEL7 数据手册 > AD5331BRU-REEL7 数据手册 10/28 页

¥ 0

AD5331BRU-REEL7 数据手册 - ADI(亚德诺)

制造商:

ADI(亚德诺)

分类:

DA转换器

封装:

TSSOP

描述:

2.5 V至5.5 V , 115 μA ,并行接口单电压输出8位/ 10位/ 12位DAC 2.5 V to 5.5 V, 115 μA, Parallel Interface Single Voltage-Output 8-/10-/12-Bit DACs

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P7P8P9P10P23Hot

典型应用电路图在P21

原理图在P1P7P8P9P10

封装尺寸在P24

型号编码规则在P25

焊接温度在P6

功能描述在P1P7P8P9P10

技术参数、封装参数在P1P3P6

应用领域在P1P21

电气规格在P13

导航目录

AD5331BRU-REEL7数据手册

Page:

of 28 Go

若手册格式错乱,请下载阅览PDF原文件

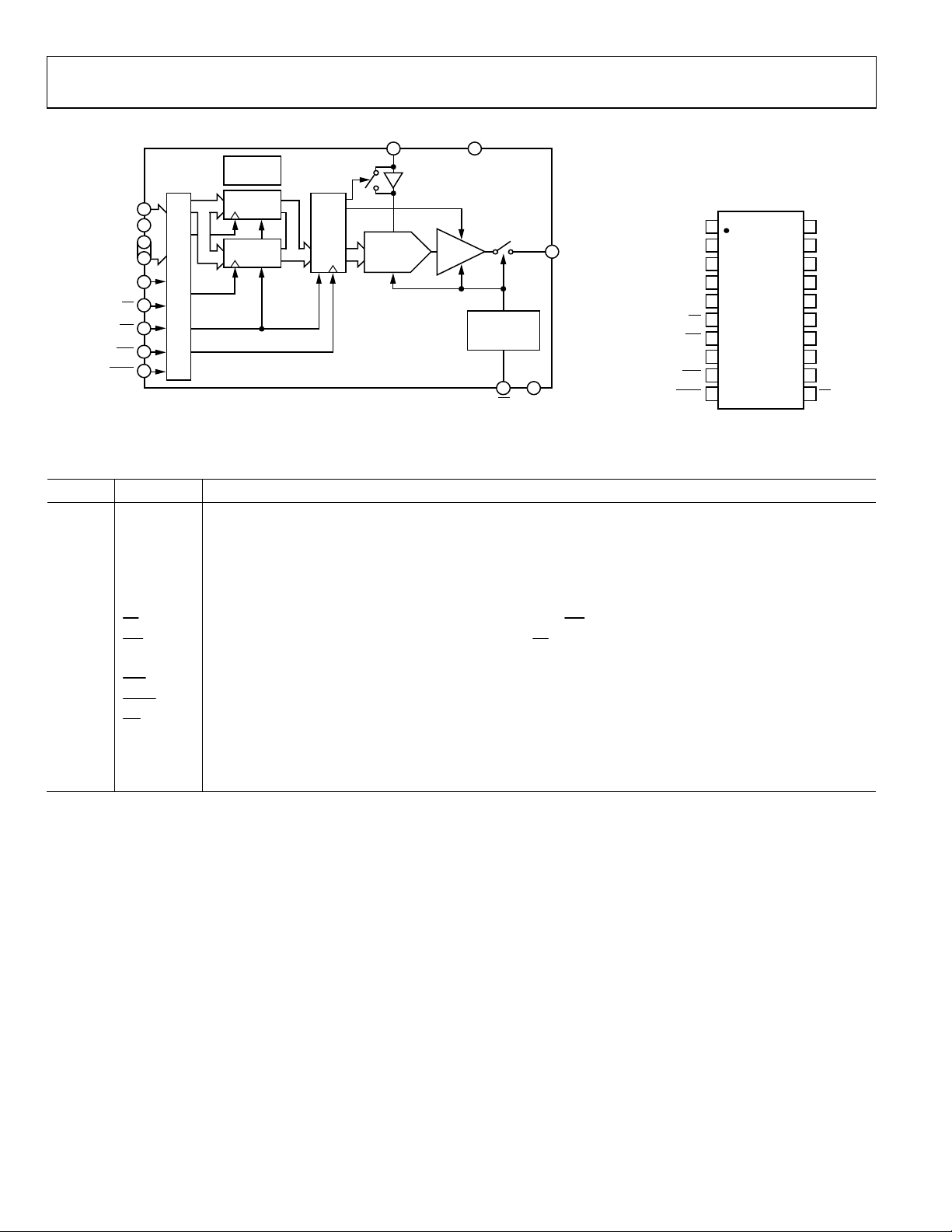

AD5330/AD5331/AD5340/AD5341

Rev. A | Page 10 of 28

BUFFER

12-BIT

DAC

DAC

REGISTER

LOW BYTE

REGISTER

INTERFACE LOGIC

POWER-DOWN

LOGIC

BUF

DB

7

DB

0

.

.

HBEN

CS

WR

CLR

LDAC

V

REF

V

DD

V

OUT

PD GND

AD5341

POWER-ON

RESET

RESET

9

7

6

1

13

20

2

GAIN

8

3 12

4

11 5

HIGH BYTE

REGISTER

10

06852-009

20

19

18

17

16

15

14

13

12

11

1

2

3

4

5

6

7

8

9

10

LDAC

GAIN

WR

CS

GND

V

REF

V

OUT

CLR

DB

7

DB

6

DB

5

DB

4

DB

3

DB

2

DB

1

DB

0

V

DD

PD

TOP VIEW

(Not to Scale)

AD5341

10-BIT

HBEN

BUF

06852-010

Figure 9. AD5341 Functional Block Diagram Figure 10. AD5341 Pin Configuration

Table 8. AD5341 Pin Function Descriptions

Pin No. Mnemonic Description

1 HBEN

High Byte Enable Pin. This pin is used when writing to the device to determine if data is written to the high

byte register or the low byte register.

2 BUF Buffer Control Pin. This pin controls whether the reference input to the DAC is buffered or unbuffered.

3 V

REF

Reference Input.

4 V

OUT

Output of DAC. Buffered output with rail-to-rail operation.

5 GND Ground reference point for all circuitry on the part.

6

CS

Active low Chip Select Input. This is used in conjunction with WR to write data to the parallel interface.

7

WR

Active Low Write Input. This is used in conjunction with CS to write data to the parallel interface.

8 GAIN Gain Control Pin. This controls whether the output range from the DAC is 0 V to V

REF

or 0 V to 2 × V

REF

.

9

CLR

Asynchronous active low control input that clears all input registers and DAC registers to zero.

10

LDAC

Active low control input that updates the DAC registers with the contents of the input registers.

11

PD

Power-Down Pin. This active low control pin puts the DAC into power-down mode.

12 V

DD

Power Supply Input. These parts can operate from 2.5 V to 5.5 V and the supply should be decoupled with a

10 μF capacitor in parallel with a 0.1 μF capacitor to GND.

13 to 20 DB

0

to DB

7

Eight Parallel Data Inputs. DB

7

is the MSB of these eight bits.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件