Datasheet 搜索 > ADI(亚德诺) > LT1169CS8#TR 数据手册 > LT1169CS8#TR 数据手册 2/12 页

器件3D模型

器件3D模型¥ 32.337

LT1169CS8#TR 数据手册 - ADI(亚德诺)

制造商:

ADI(亚德诺)

封装:

SOP

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

典型应用电路图在P10P11P12

技术参数、封装参数在P1

应用领域在P10P11P12

导航目录

LT1169CS8#TR数据手册

Page:

of 12 Go

若手册格式错乱,请下载阅览PDF原文件

2

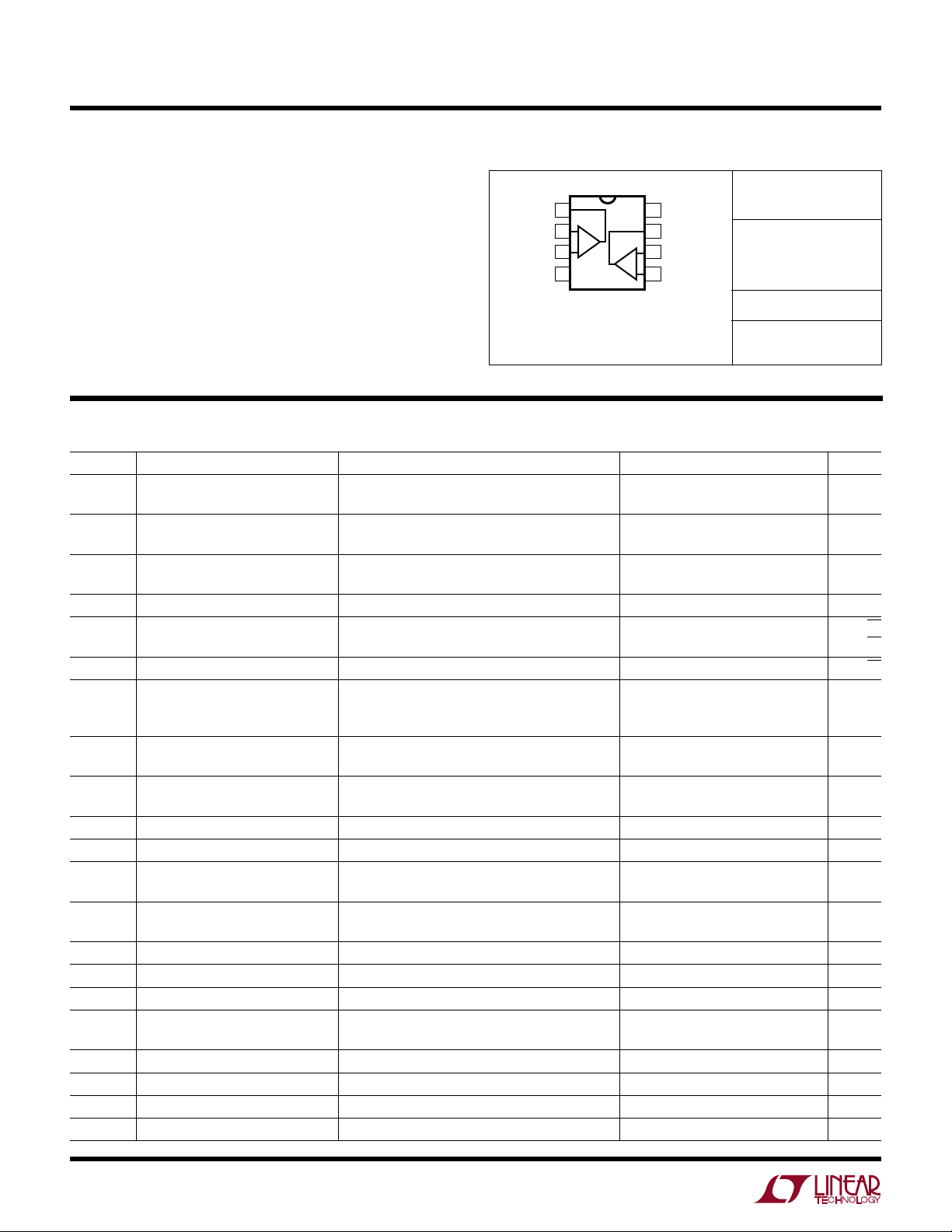

LT1169

ORDER PART

NUMBER

A

U

G

W

A

W

U

W

ARB

S

O

LU

T

EXI T

I

S

Supply Voltage

–55°C to 105°C ............................................... ±20V

105°C to 125°C ............................................... ±16V

Differential Input Voltage ...................................... ±40V

Input Voltage (Equal to Supply Voltage)............... ±20V

Output Short-Circuit Duration......................... Indefinite

Operating Temperature Range............... – 40°C to 85°C

Storage Temperature Range................ –65°C to 150°C

Lead Temperature (Soldering, 10 sec) ................ 300°C

WU

U

PACKAGE

/

O

RDER I FOR ATIO

S8 PART MARKING

LT1169CN8

LT1169CS8

T

JMAX

= 150°C, θ

JA

= 80°C/W (N8)

T

JMAX

= 160°C, θ

JA

= 190°C/W (S8)

Consult factory for Industrial and Military grade parts.

V

S

= ±15V, V

CM

= 0V, T

A

= 25°C, unless otherwise noted.

E

LECTR

IC

AL C CHARA TERIST

ICS

SYMBOL PARAMETER CONDITIONS (Note 1) MIN TYP MAX UNITS

V

OS

Input Offset Voltage 0.60 2.0 mV

V

S

= ±5V 0.65 2.2 mV

I

OS

Input Offset Current Warmed Up (Note 2) 2.5 15 pA

T

J

= 25°C (Note 5) 0.7 4 pA

I

B

Input Bias Current Warmed Up (Note 2) 4.0 20 pA

T

J

= 25°C (Note 5) 1.5 5 pA

e

n

Input Noise Voltage 0.1Hz to 10Hz 2.4 µV

P-P

Input Noise Voltage Density f

O

= 10Hz 17 nV/√Hz

f

O

= 1000Hz 6 8 nV/√Hz

i

n

Input Noise Current Density f

O

= 10Hz, f

O

= 1kHz (Note 3) 1 fA/√Hz

R

IN

Input Resistance

Differential Mode 10

14

Ω

Common Mode V

CM

= –10V to 13V 10

13

Ω

C

IN

Input Capacitance 1.5 pF

V

S

= ±5V 2.0 pF

V

CM

Input Voltage Range (Note 4) 13.0 13.5 V

–10.5 –11.0 V

CMRR Common Mode Rejection Ratio V

CM

= –10V to 13V 82 95 dB

PSRR Power Supply Rejection Ratio V

S

= ±4.5V to ±20V 83 98 dB

A

VOL

Large-Signal Voltage Gain V

O

= ±12V, R

L

= 10k 1000 4500 V/mV

V

O

= ±10V, R

L

= 1k 500 3000 V/mV

V

OUT

Output Voltage Swing R

L

= 10k ±13.0 ±13.8 V

R

L

= 1k ±12.0 ±13.0 V

SR Slew Rate R

L

≥ 2k (Note 6) 2.4 4.2 V/µs

GBW Gain-Bandwidth Product f

O

= 100kHz 3.3 5.3 MHz

Channel Separation f

O

= 10Hz, V

O

= ±10V, R

L

= 1k 126 dB

I

S

Supply Current per Amplifier 5.3 6.50 mA

V

S

= ±5V 5.3 6.45 mA

∆V

OS

Offset Voltage Match 0.8 3.5 mV

∆I

B

+

Noninverting Bias Current Match Warmed Up (Note 2) 3 20 pA

∆CMRR Common Mode Rejection Match (Note 8) 78 94 dB

∆PSRR Power Supply Rejection Match (Note 8) 80 95 dB

1169

1

2

3

4

8

7

6

5

TOP VIEW

N8 PACKAGE

8-LEAD PDIP

B

A

OUT A

–IN A

+IN A

V

–

V

+

OUT B

–IN B

+IN B

S8 PACKAGE

8-LEAD PLASTIC SO

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件