Datasheet 搜索 > 主动器件 > Maxim Integrated(美信) > MAX3815CCM+D 数据手册 > MAX3815CCM+D 数据手册 7/11 页

器件3D模型

器件3D模型¥ 133.289

MAX3815CCM+D 数据手册 - Maxim Integrated(美信)

制造商:

Maxim Integrated(美信)

分类:

主动器件

封装:

TQFP-48

描述:

Maxim Integrated### 视频,Maxim Integrated

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

MAX3815CCM+D数据手册

Page:

of 11 Go

若手册格式错乱,请下载阅览PDF原文件

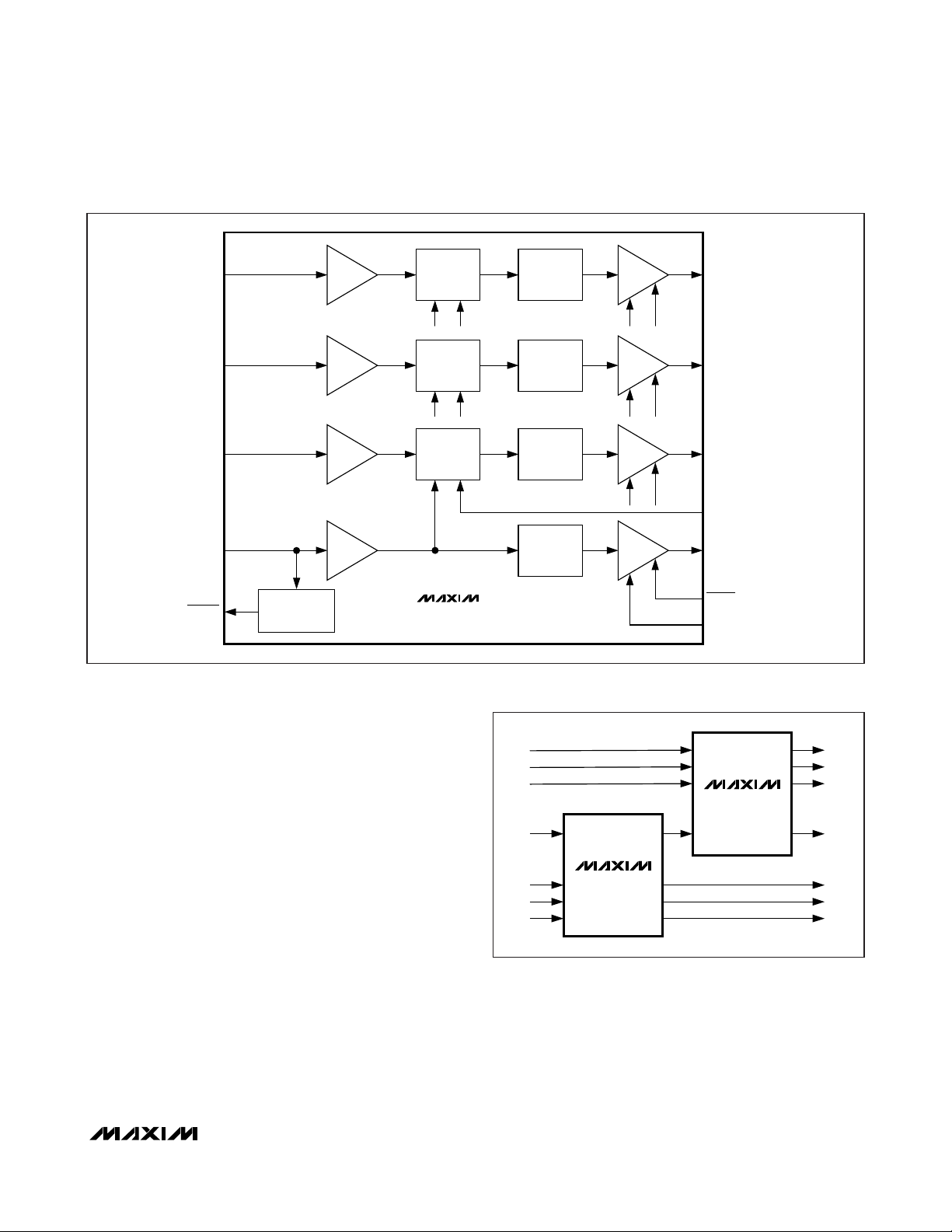

analog nVGA links, must handle a variety of resolutions

and screen update rates. The actual range of digital

serial rates is roughly 250Mbps to 1.65Gbps. For appli-

cations requiring ultra-high resolutions (e.g., QXGA), a

“double-link” TMDS interface is used and is composed

of six data links plus the clock, requiring two MAX3815

ICs with the clock going to both ICs. See Figure 2.

The MAX3815 can be used to extend any TMDS inter-

face as used under the following trademarked names:

DVI (digital visual interface), DFP™ (digital flat-panel),

PanelLink, ADC™ (Apple display connector), and

HDMI (high-definition multimedia interface).

Loss-of-Clock Signal (

CLKLOS

) Output

Loss-of-clock signal is indicated by the CLKLOS out-

put. A low level on CLKLOS indicates that the signal

power on the RXC_IN pins has dropped below a

threshold. When there is sufficient input voltage to the

channel (typically greater than 100mV

P-P

differential),

CLKLOS is high. The CLKLOS output is suitable for

indicating problems with the transmission link caused

by, for example, a broken cable, a defective driver, or a

lost connection to the equalizer.

MAX3815

TMDS Digital Video Equalizer for DVI/HDMI

Cables

_______________________________________________________________________________________ 7

INPUT

BUFFER

DRIVER

ADAPTIVE

EQ

LIMITING

AMPLIFIER

TERMINATED

3.3V CML

INPUT

BUFFER

DRIVER

ADAPTIVE

EQ

LIMITING

AMPLIFIER

TERMINATED

3.3V CML

INPUT

BUFFER

DRIVER

ADAPTIVE

EQ

LIMITING

AMPLIFIER

TERMINATED

3.3V CML

INPUT

BUFFER

DRIVER

LIMITING

AMPLIFIER

TERMINATED

3.3V CML

RXC_OUT+/-

OUTLEVEL

RX0_OUT+/-

RX1_OUT+/-

RX2_OUT+/-

RX2_IN+/-

RX1_IN+/-

RX0_IN+/-

RXC_IN+/-

CLKLOS

EQCONTROL

OUTON

CLOCK LOS

DETECTOR

MAX3815

Figure 1. Functional Diagram

MAX3815

MAX3815

D0

D1

D2

D3

D4

D5

D0

D1

D2

D3

D4

D5

CLK

CLK

Figure 2. Connection Scheme for MAX3815 in Dual Link

Application

ADC is a trademark of Apple Computer, Inc.

DFP is a trademark of Video Electronics Standards Association

(VESA).

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件