Datasheet 搜索 > 微控制器 > Microchip(微芯) > PIC18F4685-E/ML 数据手册 > PIC18F4685-E/ML 数据手册 163/484 页

器件3D模型

器件3D模型¥ 34.818

PIC18F4685-E/ML 数据手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

QFN-44

描述:

PIC18 系列 3328 B RAM 96 kB 闪存 8位 微控制器 - QFN-44

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P4P5P167P169P176Hot

典型应用电路图在P193

原理图在P10P12P13P27P43P146P150P154P160P162P168P169

封装尺寸在P459

标记信息在P457P458

封装信息在P457P459P460P461P462P463

技术参数、封装参数在P432P433P434P436P437P438

应用领域在P180P272

电气规格在P107P260P261P265P266

导航目录

PIC18F4685-E/ML数据手册

Page:

of 484 Go

若手册格式错乱,请下载阅览PDF原文件

© 2007 Microchip Technology Inc. Preliminary DS39761B-page 161

PIC18F2682/2685/4682/4685

14.2 Timer3 16-Bit Read/Write Mode

Timer3 can be configured for 16-bit reads and writes

(see Figure 14-2). When the RD16 control bit

(T3CON<7>) is set, the address for TMR3H is mapped

to a buffer register for the high byte of Timer3. A read

from TMR3L will load the contents of the high byte of

Timer3 into the Timer3 High Byte Buffer register. This

provides the user with the ability to accurately read all

16 bits of Timer1 without having to determine whether

a read of the high byte, followed by a read of the low

byte, has become invalid due to a rollover between

reads.

A write to the high byte of Timer3 must also take place

through the TMR3H Buffer register. The Timer3 high

byte is updated with the contents of TMR3H when a

write occurs to TMR3L. This allows a user to write all

16 bits to both the high and low bytes of Timer3 at once.

The high byte of Timer3 is not directly readable or

writable in this mode. All reads and writes must take

place through the Timer3 High Byte Buffer register.

Writes to TMR3H do not clear the Timer3 prescaler.

The prescaler is only cleared on writes to TMR3L.

14.3 Using the Timer1 Oscillator as the

Timer3 Clock Source

The Timer1 internal oscillator may be used as the clock

source for Timer3. The Timer1 oscillator is enabled by

setting the T1OSCEN (T1CON<3>) bit. To use it as the

Timer3 clock source, the TMR3CS bit must also be set.

As previously noted, this also configures Timer3 to

increment on every rising edge of the oscillator source.

The Timer1 oscillator is described in Section 12.0

“Timer1 Module”.

14.4 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments

from 0000h to FFFFh and overflows to 0000h. The

Timer3 interrupt, if enabled, is generated on overflow

and is latched in the interrupt flag bit, TMR3IF

(PIR2<1>). This interrupt can be enabled or disabled

by setting or clearing the Timer3 Interrupt Enable bit,

TMR3IE (PIE2<1>).

14.5 Resetting Timer3 Using the

ECCP1 Special Event Trigger

If the ECCP1 module is configured to generate a

Special Event Trigger in Compare mode

(ECCP1M3:ECCP1M0 = 1011), this signal will reset

Timer3. It will also start an A/D conversion if the A/D

module is enabled (see Section 15.3.4 “Special

Event Trigger” for more information.).

The module must be configured as either a timer or

synchronous counter to take advantage of this feature.

When used this way, the ECCPR1H:ECCPR1L register

pair effectively becomes a period register for Timer3.

If Timer3 is running in Asynchronous Counter mode,

the Reset operation may not work.

In the event that a write to Timer3 coincides with a

Special Event Trigger from a CCP1 module, the write

will take precedence.

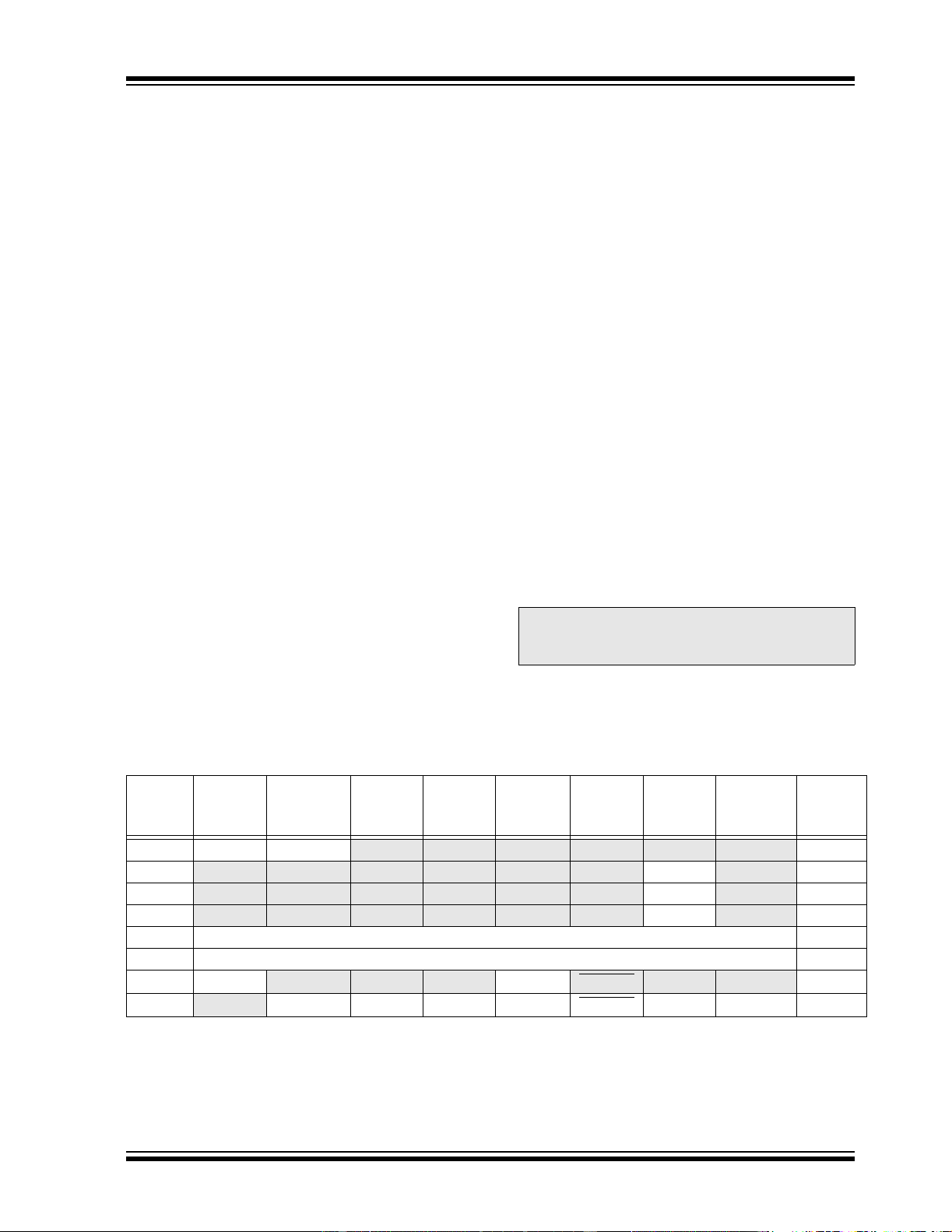

TABLE 14-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

Note: The Special Event Triggers from the

ECCP1 module will not set the TMR3IF

interrupt flag bit (PIR2<1>).

Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Reset

Values

on page

INTCON GIE/GIEH PEIE/GIEL

TMR0IE INT0IE RBIE TMR0IF INT0IF RBIF 49

PIR2 OSCFIF CMIF

(1)

— EEIF BCLIF HLVDIF TMR3IF ECCP1IF

(1)

52

PIE2

OSCFIE CMIE

(1)

— EEIE BCLIE HLVDIE TMR3IE ECCP1IE

(1)

52

IPR2

OSCFIP CMIP

(1)

— EEIP BCLIP HLVDIP TMR3IP ECCP1IP

(1)

51

TMR3L Timer3 Register, Low Byte 51

TMR3H Timer3 Register, High Byte 51

T1CON RD16

T1RUN T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON 50

T3CON

RD16 T3ECCP1

(1)

T3CKPS1 T3CKPS0 T3CCP1

(1)

T3SYNC TMR3CS TMR3ON 51

Legend: — = unimplemented, read as ‘0’. Shaded cells are not used by the Timer3 module.

Note 1: These bits are unimplemented on PIC18F2682/2685 devices; always maintain these bits clear.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件