Datasheet 搜索 > Intel(英特尔) > EP2C8F256C6N 数据手册 > EP2C8F256C6N 产品设计参考手册 4/44 页

器件3D模型

器件3D模型¥ 565.263

EP2C8F256C6N 产品设计参考手册 - Intel(英特尔)

制造商:

Intel(英特尔)

封装:

FBGA-256

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

原理图在P17

功能描述在P38

应用领域在P5P11

导航目录

EP2C8F256C6N数据手册

Page:

of 44 Go

若手册格式错乱,请下载阅览PDF原文件

transactions into your device during runtime. Because the JTAG pins are readily

accessible during runtime, this IP core enables an easy way to customize a JTAG scan

chain internal to the device, which you can then use to create debugging applications.

Examples of debugging applications include induced trigger conditions evaluated by a

Signal Tap logic analyzer by exercising test signals connected to the analyzer instance,

a replacement for a front panel interface during the prototyping phase of the design,

or inserted test vectors for exercising the design under test.

The infrastructure is an extension of the JTAG protocol for use with Intel-specific

applications and user applications, such as the Signal Tap logic analyzer.

Installing and Licensing Intel FPGA IP Cores

The Intel Quartus Prime software installation includes the Intel FPGA IP library. This

library provides many useful IP cores for your production use without the need for an

additional license. Some Intel FPGA IP cores require purchase of a separate license for

production use. The Intel FPGA IP Evaluation Mode allows you to evaluate these

licensed Intel FPGA IP cores in simulation and hardware, before deciding to purchase a

full production IP core license. You only need to purchase a full production license for

licensed Intel IP cores after you complete hardware testing and are ready to use the

IP in production.

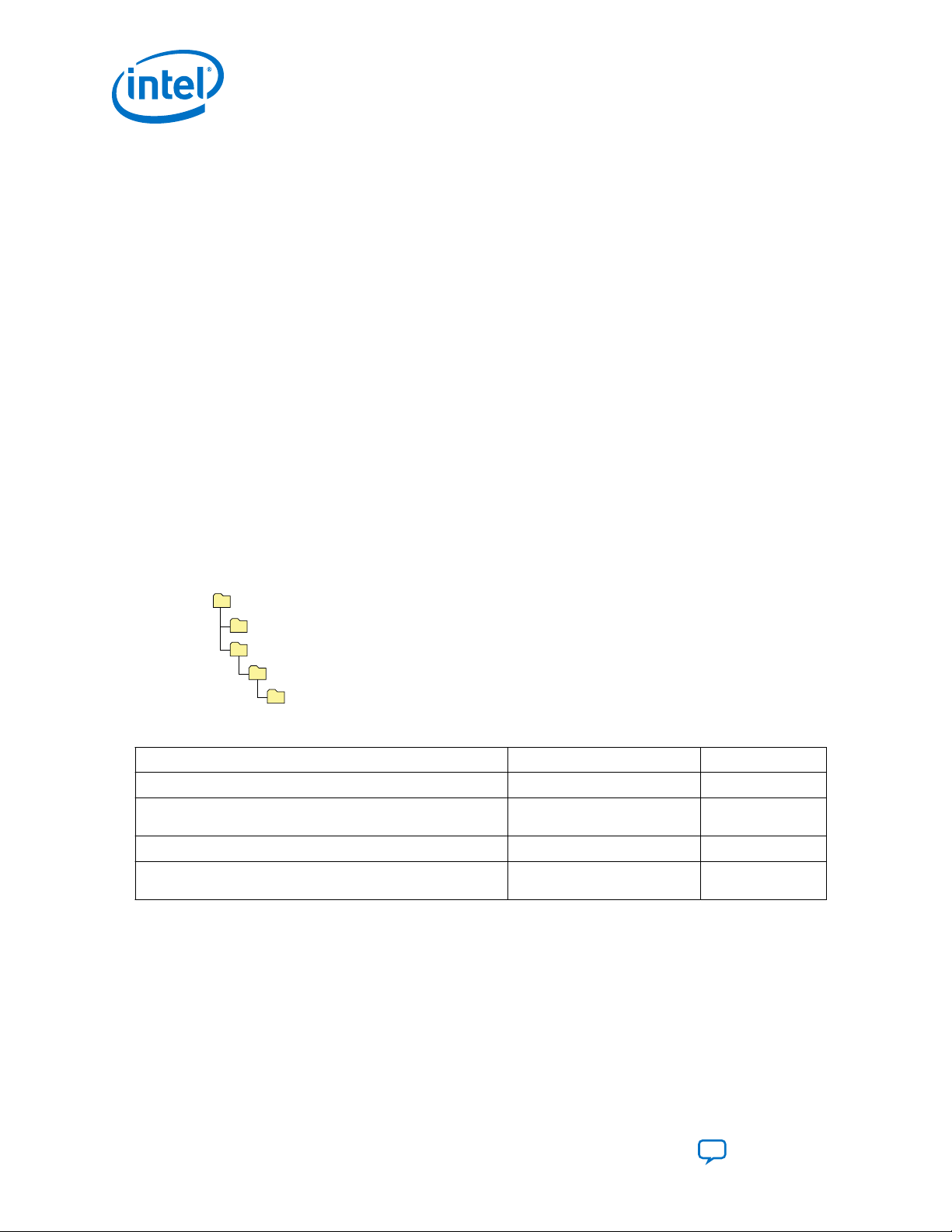

The Intel Quartus Prime software installs IP cores in the following locations by default:

Figure 1. IP Core Installation Path

intelFPGA(_pro)

quartus - Contains the Intel Quartus Prime software

ip - Contains the Intel FPGA IP library and third-party IP cores

altera - Contains the Intel FPGA IP library source code

<IP name> - Contains the Intel FPGA IP source files

Table 1. IP Core Installation Locations

Location Software Platform

<drive>:\intelFPGA_pro\quartus\ip\altera

Intel Quartus Prime Pro Edition Windows*

<drive>:\intelFPGA\quartus\ip\altera

Intel Quartus Prime Standard

Edition

Windows

<home directory>:/intelFPGA_pro/quartus/ip/altera

Intel Quartus Prime Pro Edition Linux*

<home directory>:/intelFPGA/quartus/ip/altera

Intel Quartus Prime Standard

Edition

Linux

Note: The Intel Quartus Prime software does not support spaces in the installation path.

On-Chip Debugging Tool Suite

The On-Chip Debugging Tool Suite enables real time verification of a design and

includes the following tools:

Virtual JTAG Intel

®

FPGA IP Core User Guide

UG-SLDVRTL | 2020.12.01

Virtual JTAG Intel

®

FPGA IP Core User Guide

Send Feedback

4

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件