Datasheet 搜索 > Intel(英特尔) > EP2C8F256C6N 数据手册 > EP2C8F256C6N 产品设计参考手册 5/44 页

器件3D模型

器件3D模型¥ 565.263

EP2C8F256C6N 产品设计参考手册 - Intel(英特尔)

制造商:

Intel(英特尔)

封装:

FBGA-256

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

原理图在P17

功能描述在P38

应用领域在P5P11

导航目录

EP2C8F256C6N数据手册

Page:

of 44 Go

若手册格式错乱,请下载阅览PDF原文件

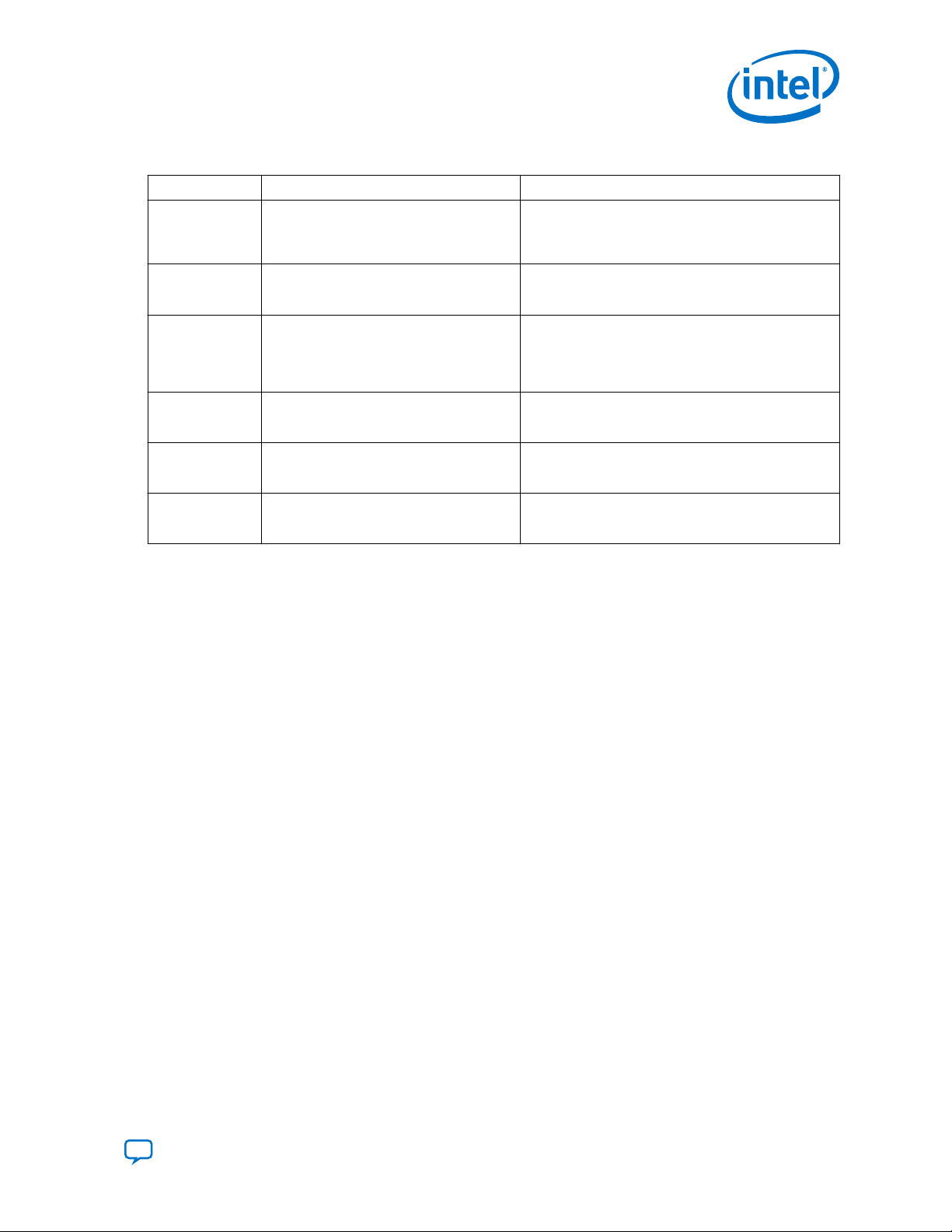

Table 2. On-Chip Debugging Tool Suite

Tool Description Typical Circumstances for Use

Signal Tap Logic

Analyzer

Uses FPGA resources to sample tests nodes

and outputs the information to the Intel

Quartus Prime software for display and

analysis.

You have spare on-chip memory and want functional

verification of your design running in hardware.

Signal Probe Incrementally routes internal signals to I/O

pins while preserving the results from your

last place-and-route.

You have spare I/O pins and want to check the

operation of a small set of control pins using either an

external logic analyzer or an oscilloscope.

Logic Analyzer

Interface (LAI)

Multiplexes a larger set of signals to a

smaller number of spare I/O pins. LAI allows

you to select which signals are switched

onto the I/O pins over a JTAG connection.

You have limited on-chip memory and have a large set

of internal data buses that you want to verify using an

external logic analyzer. Logic analyzer vendors, such as

Tektronics and Agilent, provide integration with the tool

to improve usability.

In-System

Memory

Content Editor

Displays and allows you to edit on-chip

memory.

You want to view and edit the contents of either the

instruction cache or data cache of a Nios

®

II processor

application.

In-System

Sources and

Probes

Provides a way to drive and sample logic

values to and from internal nodes using the

JTAG interface.

You want to prototype a front panel with virtual

buttons for your FPGA design.

Virtual JTAG

Interface

Opens the JTAG interface so that you can

develop your own custom applications.

You want to generate a large set of test vectors and

send them to your device over the JTAG port to

functionally verify your design running in hardware.

Related Information

Intel Quartus Prime Standard Edition User Guide: Debug Tools

Applications of the Virtual JTAG Intel FPGA IP Core

You can instantiate single or multiple instances of the Virtual JTAG Intel FPGA IP core

in your HDL code. During synthesis, the Intel Quartus Prime software assigns unique

IDs to each instance, so that each instance is accessed individually. You can

instantiate up to 128 instances of the Virtual JTAG Intel FPGA IP core. The figure

below shows a typical application in a design with multiple instances of the IP core.

Virtual JTAG Intel

®

FPGA IP Core User Guide

UG-SLDVRTL | 2020.12.01

Send Feedback

Virtual JTAG Intel

®

FPGA IP Core User Guide

5

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件