Datasheet 搜索 > 逻辑控制器 > TI(德州仪器) > SN74LVC2G07YZPR 数据手册 > SN74LVC2G07YZPR 数据手册 10/27 页

器件3D模型

器件3D模型¥ 1.115

SN74LVC2G07YZPR 数据手册 - TI(德州仪器)

制造商:

TI(德州仪器)

分类:

逻辑控制器

封装:

DSBGA-6

描述:

双缓冲/驱动器,具有漏极开路输出 DUAL BUFFER/DRIVER WITH OPEN-DRAIN OUTPUTS

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P3Hot

典型应用电路图在P9P10

原理图在P1P8

封装尺寸在P12P14P15P24

焊盘布局在P25

标记信息在P12P13

封装信息在P11P12P13P14P15

技术参数、封装参数在P4P9

应用领域在P1P13

电气规格在P5

型号编号列表在P9

导航目录

SN74LVC2G07YZPR数据手册

Page:

of 27 Go

若手册格式错乱,请下载阅览PDF原文件

V

CC

Unused Input

Input

Output Output

Input

Unused Input

Vcc - V

TPD - ns

0 1 2 3 4 5 6

0

1

2

3

4

5

6

D002

TPD

10

SN74LVC2G07

SCES308L –AUGUST 2001–REVISED MAY 2015

www.ti.com

Product Folder Links: SN74LVC2G07

Submit Documentation Feedback Copyright © 2001–2015, Texas Instruments Incorporated

Typical Application (continued)

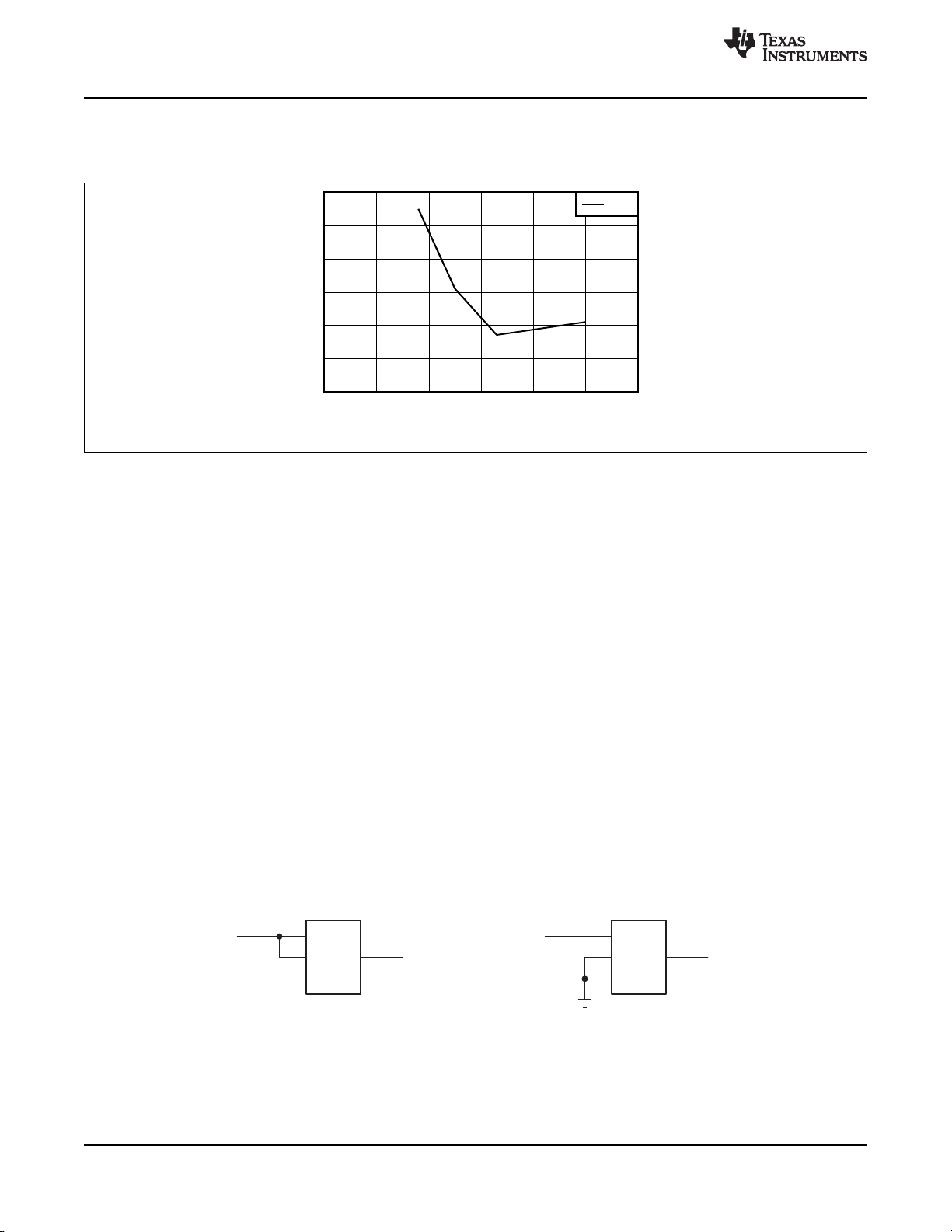

9.2.3 Application Curve

Figure 4. TPD Across V

CC

at 25°C

10 Power Supply Recommendations

The power supply can be any voltage between the minimum and maximum supply voltage rating located in the

Recommended Operating Conditions table.

Each V

CC

pin should have a good bypass capacitor to prevent power disturbance. For devices with a single

supply a 0.1-μF capacitor is recommended and if there are multiple V

CC

pins then a 0.01-μF or 0.022-μF

capacitor is recommended for each power pin. It is ok to parallel multiple bypass caps to reject different

frequencies of noise. 0.1-μF and 1-μF capacitors are commonly used in parallel. The bypass capacitor should be

installed as close to the power pin as possible for best results.

11 Layout

11.1 Layout Guidelines

When using multiple bit logic devices inputs should not ever float. In many cases, functions or parts of functions

of digital logic devices are unused; for example, when only two inputs of a triple-input AND gate are used or only

3 of the 4 buffer gates are used. Such input pins should not be left unconnected because the undefined voltages

at the outside connections result in undefined operational states. Specified below are the rules that must be

observed under all circumstances. All unused inputs of digital logic devices must be connected to a high or low

bias to prevent them from floating. The logic level that should be applied to any particular unused input depends

on the function of the device. Generally they will be tied to GND or V

CC

whichever make more sense or is more

convenient.

11.2 Layout Examples

Figure 5. Layout Examples for SN74LVC2G07

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件